Voici la structure de données du segment d'état de tâche (Task State Segment) qu'utilise les microprocesseurs 80286 ou supérieur.

Format du TSS du 80286

| Déplacement | Type de données | Description |

|---|---|---|

| +00h | WORD | Sélecteur TSS précédent (lien par arrière). |

| +02h | WORD | Déplacement dans la pile de l'anneau 0 |

| +04h | WORD | Sélecteur de la pile de l'anneau 0 |

| +06h | WORD | Déplacement dans la pile de l'anneau 1 |

| +08h | WORD | Sélecteur de la pile de l'anneau 1 |

| +0Ah | WORD | Déplacement dans la pile de l'anneau 2 |

| +0Ch | WORD | Sélecteur dans la pile de l'anneau 2 |

| +0Eh | WORD | Registre IP |

| +10h | WORD | Registre des drapeaux |

| +12h | WORD | Registre AX |

| +14h | WORD | Registre CX |

| +16h | WORD | Registre DX |

| +18h | WORD | Registre BX |

| +1Ah | WORD | Registre SP |

| +1Ch | WORD | Registre BP |

| +1Eh | WORD | Registre SI |

| +20h | WORD | Registre DI |

| +22h | WORD | Registre ES |

| +24h | WORD | Registre CS |

| +26h | WORD | Registre SS |

| +28h | WORD | Registre DS |

| +2Ah | WORD | Registre LDT |

| La longueur de cette structure de données est de 44 octets ou 2Ch en hexadécimal. | ||

Format du TSS du 80386

| Déplacement | Type de données | Description |

|---|---|---|

| +00h | DWORD | 0000h/Sélecteur TSS précédent (lien par arrière). |

| +04h | DWORD | Pointeur de pile pour l'anneau 0 |

| +08h | DWORD | 0000h/Sélecteur de pile pour l'anneau 0 |

| +0Ch | DWORD | Pointeur de pile pour l'anneau 1 |

| +10h | DWORD | 0000h/Sélecteur de pile pour l'anneau 1 |

| +14h | DWORD | Pointeur de pile pour l'anneau 2 |

| +18h | DWORD | 0000h/Sélecteur de pile pour l'anneau 2 |

| +1Ch | DWORD | Registre CR3 |

| +20h | DWORD | Registre EIP |

| +24h | DWORD | Registre des drapeaux EFLAGS |

| +28h | DWORD | Registre EAX |

| +2Ch | DWORD | Registre ECX |

| +30h | DWORD | Registre EDX |

| +34h | DWORD | Registre EBX |

| +38h | DWORD | Registre ESP |

| +3Ch | DWORD | Registre EBP |

| +40h | DWORD | Registre ESI |

| +44 | DWORD | Registre EDI |

| +48 | DWORD | 0000h/Registre ES |

| +4C | DWORD | 0000h/Registre CS |

| +50 | DWORD | 0000h/Registre SS |

| +54 | DWORD | 0000h/Registre DS |

| +58 | DWORD | 0000h/Registre FS |

| +5C | DWORD | 0000h/Registre GS |

| +60 | DWORD | 0000h/LDT |

| +64 | WORD | Bits de trappe |

| +66 | WORD | Déplacement dans le TSS vers la cartographie des autorisations d'entrée/sortie |

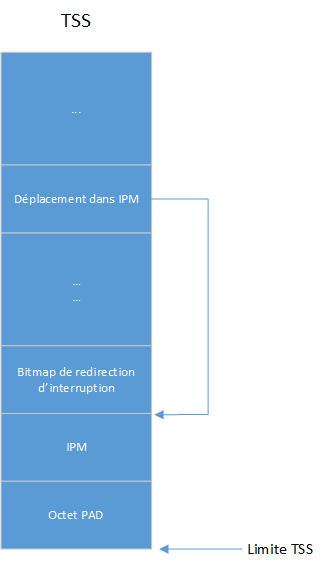

| La longueur minimal de la structure de données TSS est de 104 octets ou 68h en hexadécimal. L'IPM est l'adresse de base de la cartographie de permission d'entrée/sortie. TSS_LAST est le dernier octet de TSS. | ||

| +IPM-20h | 32 octets (20h) | Bitmap de redirection d'interruption logicielle (VME) 1 bit/int |

| +IPM | xx octets | Bitmap de permission d'entrée/sortie 1 bit/port |

| +TSS_LAST | xx octets | Octet de PAD d'entrée/sortie. Octet PAD indique quels bits du dernier octet de bitmap autorise la validation de l'entrée/sortie. Recommandé de mettre cet octet en FFh. |

Dernière mise à jour : Lundi, le 20 mai 2019