Introduction

La puce 6508 de l'entreprise MOS Technologie est un microprocesseur à faible coût capable de répondre aux exigences des petits systèmes et de problèmes de contrôle périphérique à un coût minimum pour l'utilisateur. Une page complète (soit 256 octets) de RAM est située (directement sur la puce) simultanément à la page 0 et la page 1 permettant l'adressage de page 0 et les opérations de pile sans RAM supplémentaire. Un port d'entrée/sortie bidirectionnel à 8 bits est intégré sur la puce avec le registre de sortie à l'adresse 0001. Le port d'entrée/sortie est programmable bit par bit. Le registre de direction des données est à l'adresse 0000. Le bus d'adresses à 16 bits à 3 états permet l'accès direct à la mémoire (DMA) et les systèmes multiprocesseurs partageant une mémoire commune. L'architecture de processeur interne est identique au 6502 de Commodore Semiconductor Group pour fournir une compatibilité logicielle.

Fiche technique

Voici les caractéristiques de la puce «6508» de «MOS Technology»:

| Spécification | Description |

|---|---|

| Concepteur | MOS Technology |

| Modèle | 6508 |

| RAM intégré | 256 octets |

| Alimentation | +5 Volts |

| Nombre d'instructions | 56 |

| Compatibilité | Bus compatible avec le M6800 |

| Cadencé à | 6508 à 1 MHz, 6508A à 2 MHz et 6508B à 3 MHz |

| Supplément | Port d'entrée/sortie bidirectionnel Canal N, porte de silicium, technologie de charge d'appauvrissement Traitement parallèle à 8 Instruction d'arithmétique décimale et binaire 13 modes d'adressages Véritable capacité d'indexation Pointeur de pile programmable Pile de longueur variable Capacité d'interruption Bus de données bidirectionnel à 8 bits Plage de mémoire adressable à 64 Ko Capacité d'accès direct à la mémoire Architecture pileline Utilisable avec n'importe quel type ou vitesse de mémoire |

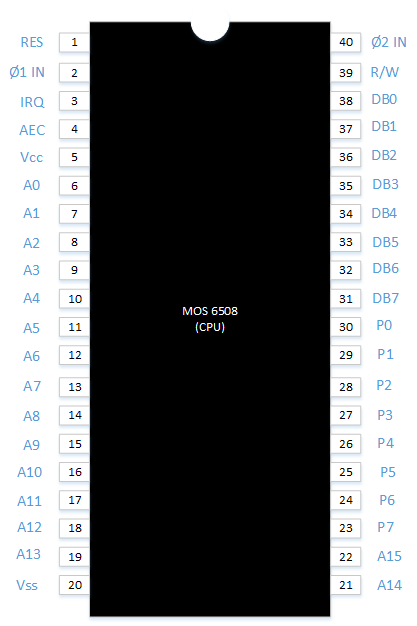

Schéma des broches

Voici le schéma des broches de la puce 6508 de l'entreprise MOS Technology :