Introduction

Le microprocesseur Intel 4040 de l'entreprise Intel est un microprocesseur compatible avec le microprocesseur 4004 mais il dispose de 16 instructions assembleurs supplémentaires (HLT, BBS, LCR, OR4, OR5, AN6, AN7, DB0, DB1, SB0, EIN, DIN, RPM) 46 déjà présente dans le 4004.

Fiche technique

Voici les caractéristiques de la puce «4040» de «Intel»:

| Spécification | Description |

|---|---|

| Fabricant | Intel |

| Modèle | 4040 |

| Nombre d'instructions | 60 |

| Nombre de registres | 24 |

| Mémoire adressable | 8 Kilooctets |

| Cadencé à | 740 kHz |

| Alimentation | 0,9 Watts |

| Date de conception | 1972 |

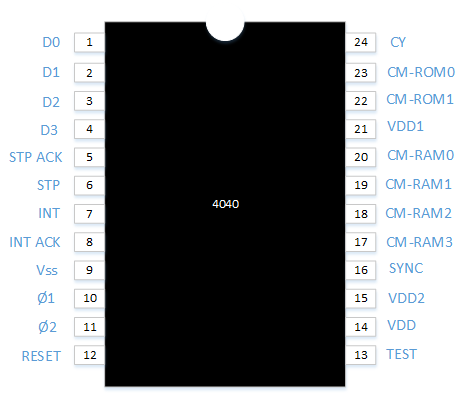

Schéma des broches

Voici le schéma des broches de la puce 4040 de l'entreprise Intel :

| Symbole | Broches | Type | Description |

|---|---|---|---|

| D0 à D3 | 1 à 4 | Entrée/sortie | BUS DE DONNÉES BIDIRECTIONNEL : Toutes les communications d'adresses et des données passant entre le processeur et les puces de RAM et de ROM se produisent par ses 4 broches. |

| RESET | 12 | Entrée | REINITIALISE : Un niveau logique 1 dans cette entrée efface tous les drapeaux et les registres d'état et force le compteur de programme à passer à la valeur 0. |

| STP | 6 | Entrée | ARRET : Un niveau logique 1 dans cette entrée indique au microprocesseur d'entrée en mode STOP. |

| STP ACK | 13 | Sortie | ARRET DE CONNAISSANCE : Ce signal est présent quand le processeur est en état d'arrêt. La sortie est en mode «drain ouvert» nécessitant une résistance de pull-down à VDD. |

| INT | 7 | Entrée | INTERRUPTION : Un niveau logique 1 dans cette entrée indique au processeur à entrer en mode d'interruption. |

| INT ACK | 8 | Sortie | INTERRUPTION RECONNAISSANCE : Ce signal accuse réception d'un signal d'INTERRUPTION et empêche des INTERRUPTIONS supplémentaires d'entrer dans le processeur. Il reste actif jusqu'à ce qu'il soit effacé par l'exécution des nouvelles instructions BRANCH BACK et SRC (BBS). La sortie est «drain ouvert» nécessitant une résistance pull-down à VDD. |

| RESET | 12 | Entrée | REINITIALISE : Un niveau logique 1 sur cette entrée efface tous les registres et les registres d'état et force le compteur du programme à 0. Pour effacer complètement tous les registres d'adresses et d'index, RESET doit être appliqué pendant 96 cycles d'horloge (12 cycles machine). |

| TEST | 13 | Entrée | REINITIALISE : L'état logique de ce signal peut être testé avec l'instruction JCN. |

| SYNC | 16 | Sortie | SYNCHRONISATION : Synchronisation du signal généré par le processeur et fixe les puces ROM et RAM. Il indique le début d'un cycle d'instruction. |

| CM-ROM0 à CM-ROM1 | 22 à 23 | Sortie | CM-ROM : C'est le signal de sélection de la ROM envoyé vers le processeur quand les données sont requises par la mémoire du programme. |

| CM-RAM0 à CN0-RAM3 | 17 à 20 | Sortie | CM-RAM : Ce sont les signaux de sélection de banque pour les puces de RAM 4002 dans le système. |

| CY | 24 | Sortie | Retenue : L'état de la retenue flip-flop est présent sur cette sortie et mis à jour à chaque fois X1. La sortie est «drain ouvert» nécessitant une résistance de traction vers le VDD. |

| Ø1 à Ø2 | 10 à 11 | Entrée | Ø1-Ø2 : Ces broches sont les 2 phases d'horloge. |

| Vss | 9 | Cet broche permet d'indiquer le voltage positif | |

| VDD | 14 | Cet broche permet d'indiquer le voltage d'alimentation principal : -15 +/- 5% |

Voir également

Articles - Les géants de l'informatique - Intel

Dernière mise à jour : Mercredi, le 16 août 2017