Introduction

Le microprocesseur 6510 de l'entreprise Commodore Semiconductor Group est un microprocesseur connu pour avoir été vendu les Commodore 64. Le 6510 est un microprocesseur à faible coût capable de résoudre un large éventail de problèmes de petits systèmes et de contrôle périphérique à un coût minimum pour l'utilisateur. Un port d'entrée/sortie bidirectionnel à 8 bits est situé sur la puce avec le registre de sortie à l'adresse 0001 et le registre de direction des données à l'adresse 0000. Le port d'entrée/sortie est programmable bit par bit. Le bus d'adresses 16 bits à trois états permet l'accès direct à la mémoire (DMA) et les systèmes multiprocesseurs partageant une mémoire commune. L'architecture du processeur interne est identique au 6502 de Commodore Semiconductor Group pour assurer la compatibilité logicielle.

Fiche technique

Voici les caractéristiques de la puce «6510» de «MOS Technology» :

| Spécification | Description |

|---|---|

| Concepteur | Commodore Semiconductor Group |

| Fabricant | Commodore Business Machine |

| Modèle | 6510 |

| Date de conception | 1982 |

| Traitement | Parallèle 8 bits |

| Bus de données | Bidirectionnel 8 bits |

| Bus d'adressage | 16 bits |

| Cadencé à | 1 Mhz, 2 Mhz ou 3 Mhz. A partir de 1986, il est également disponible à 4 Mhz. |

| Port d'entrée/sortie | Bidirectionnel 8 bits |

| Alimentation | Simple +5 volts |

| Composition | HMOS, grille de silicium, technologie de charge d'épuisement |

| Ensemble d'instruction | 56 instructions compatible au 6502 |

| Arithmétique | Décimale et binaire |

| Modes d'adressages | Treize modes d'adressage, véritable capacité d'indexation, pointeur de pile programmable |

| Pile de données | Pile de longueur variable |

| Interruption | Capacité d'interruption |

| Adressage mémoire | Intervalle de mémoire adressable jusqu'à 65 Ko, capacité d'accès direct à la mémoire |

| Architecture | Bus compatible avec M6800, Architecture de pipeline, utilisable avec n'importe quel type ou mémoire de vitesse |

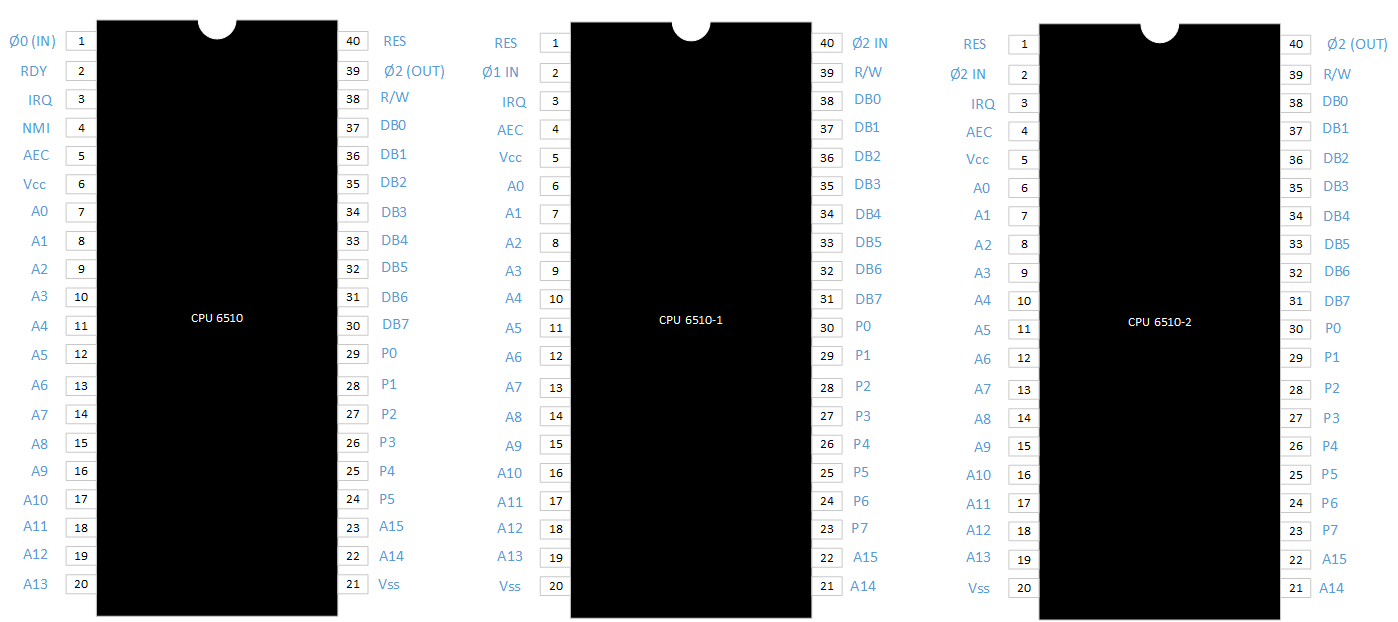

Schéma des broches

Voici le schéma des broches de la puce 6510 de l'entreprise Commodore Semiconductor Group :

Programmation

| Langage | Description |

|---|---|

| Assembleur 6502 | Langage Assembleur pour le microprocesseur 6502 |

Modes d'adressage

| Mode d'adressages | Description |

|---|---|

| Adressage de l'accumulateur | Ce format d'adressage est représentée par une instruction d'un octet, impliquant une opération sur l'accumulateur. |

| Adressage immédiat | Dans l'adressage immédiat, l'opérande est contenu dans le deuxième octet de l'instruction, sans autre adressage mémoire requis. |

| Adressage absolu | En adressage absolu, le deuxième octet de l'instruction spécifie les huit bits de poids faible de l'adresse effective tandis que le troisième octet spécifie les huit bits de poids fort. Ainsi, le mode d'adressage absolu permet d'accéder à l'intégralité des 65 K octets de la mémoire adressable. |

| Adressage de page zéro | Les instructions de page zéro permettent un code et des temps d'exécution plus courts en ne récupérant que le deuxième octet de l'instruction et en supposant un octet d'adresse haute zéro. Une utilisation prudente de la page zéro peut entraîner une augmentation significative de l'efficacité du code. |

| Adressage de page zéro indexé - (indexation X, Y) | Cette forme d'adressage est utilisée en conjonction avec le registre d'index et est appelée "Page zéro, X" ou "Page zéro, Y". L'adresse effective est calculée en ajoutant le deuxième octet au contenu du registre d'index. Puisqu'il s'agit d'une forme d'adressage «Zero Page», le contenu du deuxième octet fait référence à un emplacement dans la page zéro. De plus, en raison de la nature d'adressage « Page zéro » de ce mode, aucun report n'est ajouté aux 8 bits de mémoire de poids fort et le franchissement des limites de la page ne se produit pas. |

| Adressage d'index absolue - (indexation X, Y) | Cette forme d'adressage est utilisée en conjonction avec les registres d'index X et Y et est appelée "Absolue, X" et "Absolue, Y." L'adresse effective est formée en ajoutant le contenu de X et Y à l'adresse contenue dans les deuxième et troisième octets de l'instruction. Ce mode permet au registre d'index de contenir la valeur d'index ou de comptage et l'instruction de contenir la base. Ce type d'indexation permet à n'importe quel emplacement de référencement et à l'index de modifier plusieurs champs, ce qui réduit le temps de codage et d'exécution. |

| Adresse implicite | Dans le mode d'adressage implicite, l'adresse contenant l'opérande est implicitement indiquée dans le code opération de l'instruction. |

| Adresse relative | L'adressage relatif est utilisé uniquement avec les instructions de branchement et établit une destination pour le branchement conditionnel. Le deuxième octet de l'instruction devient l'opérande étant un «Déplacement» ajouté au contenu des huit bits inférieurs du compteur de programme lorsque le compteur est défini à l'instruction suivante. La plage de l'offset est de -128 à +127 octets de l'instruction suivante. |

| Adressage indirect indexé | Dans l'adressage indirect indexé (appelé [Indirect, X]), le deuxième octet de l'instruction est ajouté au contenu du registre d'index .X, éliminant le report. Le résultat de cet ajout pointe vers un emplacement mémoire sur la page zéro dont le contenu est les huit bits de poids faible de l'adresse effective. L'emplacement mémoire suivant dans la page zéro contient les huit bits de poids fort de l'adresse effective. Les deux emplacements mémoire spécifiant les octets de poids fort et de poids faible de l'adresse effective doivent être à la page zéro. |

| Adressage indirect indexé | En adressage indexé indirect (appelé (Indirect, Y]), le deuxième octet de l'instruction pointe vers un emplacement mémoire de la page zéro. Le contenu de cet emplacement mémoire est ajouté au contenu du registre d'index Y, le résultat étant les huit bits de poids faible de l'adresse effective.Le report de cet ajout est ajouté au contenu de l'emplacement mémoire de la page zéro suivante, le résultat étant les huit bits de poids fort de l'adresse effective. |

| Indirect absolu | Le deuxième octet de l'instruction contient les huit bits de poids faible d'un emplacement mémoire. Les huit bits de poids fort de cet emplacement mémoire sont contenus dans le troisième octet de l'instruction. Le contenu de l'emplacement mémoire entièrement spécifié est l'octet de poids faible de l'adresse effective. L'emplacement mémoire suivant contient l'octet de poids fort de l'adresse effective qui est chargé dans les seize bits du compteur de programme. |

Voir également

Langage de programmation - Turbo Pascal - Émulateur - Émulateur de microprocesseur 6502