Introduction

Le microprocesseur 8088A de l'entreprise Intel est une version 8 bits bas de gamme du microprocesseur 8086. De plus, la «prefetch input queue» du microprocesseur n'est que de 4 octets plutôt que de 8 octets, elle est donc réduite à la taille de la plus grande instruction de code machine. L'Intel 8088A est un microprocesseur intégrant la technologie de portage en silicium (HMOS-II), à canal N, avec une charge d'appauvrissement, et est emballé dans un boîtier CERDIP à 40 broches. Le processeur possède des attributs des microprocesseurs 8 et 16 bits. Il est directement compatible avec le logiciel 8086 et le matériel et les périphériques du 8080/8085.

Fiche technique

Voici les caractéristiques de la puce «8088A» de «Intel» :

| Spécification | Description |

|---|---|

| Fabricant | Intel |

| Modèle | 8088A |

| Date de conception | Juin 1979 |

| Cadencé à | 8088A (5 MHz), 8088A-2 (8 MHz) |

| Bus de données | 8 bits |

| Architecture interne | 16 bits |

| Bus d'adressage | 20 bits |

| Registres | 14 mots par ensemble de 16 bits de registres avec des opérations symétriques |

| Taille des opérations | Octet, mot ou par bloc |

| Opérations | 8 bits et 16 bits signé (entier) ou non-signé (naturel), arithmétique binaire ou décimal, incluant les multiplications et les divisions. |

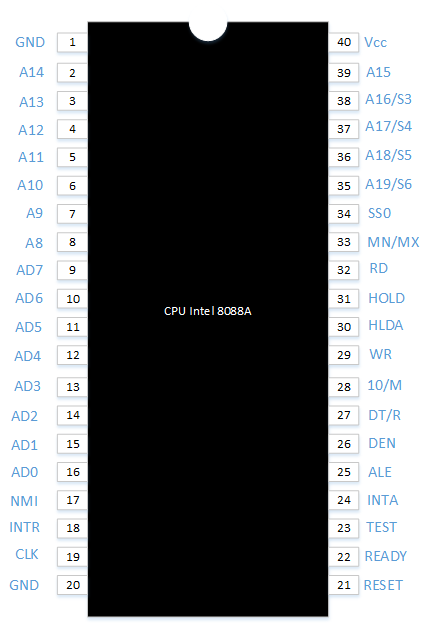

Schéma des broches

Voici le schéma des broches de la puce 8088A de l'entreprise Intel :

Les descriptions de fonction de broche suivantes concernent les systèmes 8088A en mode minimum ou maximum. Le «bus local» dans ces descriptions est la connexion d'interface de bus multiplexée directe au 8088 (sans tenir compte des tampons de bus supplémentaires).

| Symbole | Broches | Type | Description |

|---|---|---|---|

| AD7 à AD0 | 9 à 16 | Entrée/sortie | BUS DE DONNÉES D'ADRESSE : Ces broches constituent la mémoire multiplexée temporelle / adresse d'entrée/sortie (T1) et le bus de données (T2, T3, Tw, T4). Ces broches sont actives HIGH et passent à l'état 3 OFF pendant la résolution de l'interruption et le bus local reçoit un «Accusé de réception». |

| A15 à A8 | 2 à 8, 39 | Sortie | BUS D'ADRESSE : Ces broches fournissent des bits d'adresse de 8 à 15 pour tout le cycle de bus (T1 à T4). Ces broches ne doivent pas être verrouillées par ALE pour rester valides. A15 à A8 sont actives HIGH et passent à l'état 3 OFF pendant la résolution de l'interruption et le bus local reçoit un «Accusé de réception». |

| A19/S6, A18/S5, A17/S4, A16/S3 |

35 à 38 | Sortie | ADRESSE / ÉTAT : Pendant T1, ce sont les 4 broches d'adresse les plus significatives pour les opérations de mémoire. Pendant les opérations d'entrée/sortie, ces broches sont LOW. Pendant les opérations de mémoire et d'entrée/sortie, les informations d'état sont disponibles sur ces lignes pendant T2, T3, Tw et T4. S6 est toujours LOW. L'état du bit indicateur de validation d'interruption (S5) est mis à jour au début de chaque cycle d'horloge. S4 et S3 sont codés comme indiqué. Cette information indique quel registre de segment est actuellement utilisé pour l'accès aux données. Ces broches passe à 3 états OFF pendant que le bus local reçoit un «Accusé de réception». |

| RD | 32 | Sortie | LECTURE : La broche de lecture indique que le processeur effectue un cycle de lecture de mémoire ou d'entrée/sortie, selon l'état de la broche IO/M ou S2. Ce signal est utilisé pour lire les périphériques résidant sur le bus local 8088. RD est actif au niveau bas pendant T2, T3 et Tw de n'importe quel cycle de lecture, et il est garanti qu'il restera HIGH dans T2 jusqu'à ce que le bus local 8088 ait passé. Ce signal passe à 3 états OFF lorsqu'il reçoit un «Accusé de réception». |

| READY | 22 | Entrée | PRET : Cette broche est un accusé de réception de la mémoire adressée ou du périphérique d'entrée/sortie pour terminer le transfert de données. Le signal RDY de la mémoire ou des entrée/sortie est synchronisé par le générateur d'horloge 8284 pour former READY. Ce signal est actif HIGH. L'entrée 8088 READY n'est pas synchronisée. Un fonctionnement correct n'est pas garanti si les temps d'établissement et de maintien ne sont pas respectés. |

| INTR | 18 | Entrée | REQUETE D'INTERRUPTION : Cette broche est une entrée déclenchée par niveau étant échantillonnée pendant le dernier cycle d'horloge de chaque instruction pour déterminer si le processeur doit entrer dans une opération d'accusé de réception d'interruption. Un sous-programme est vectorisé via une table de recherche de vecteurs d'interruption située dans la mémoire du système. Il peut être masqué en interne par le logiciel en réinitialisant le bit de validation d'interruption. INTR est synchronisé en interne. Ce signal est actif HIGH. |

| TEST | 23 | Entrée | TEST : Cette broche est une entrée examinée par l'instruction «attente pour un test». Si l'entrée TEST est LOW, l'exécution continue, sinon le processeur attend dans un état inactif. Cette entrée est synchronisée en interne pendant chaque cycle d'horloge en frontal de CLK. |

| NMI | 17 | Entrée | INTERRUPTION NON-MASQUABLE : Cette broche est une entrée déclenchée en frontal provoquant une interruption de type 2. Un sous-programme est vectorisé via une table de recherche de vecteurs d'interruption située dans la mémoire du système. NMI n'est pas masquable en interne par logiciel. Une transition de LOW à HIGH déclenche l'interruption à la fin de l'instruction en cours. Cette entrée est synchronisée en interne. |

| RESET | 21 | Entrée | RÉINITIALISE : Cette broche provoque le processeur pour terminer immédiatement son activité actuelle. Le signal doit être actif HIGH pendant au moins 4 cycles d'horloge. Il redémarre l'exécution, comme décrit dans la description de l'ensemble d'instructions, lorsque RESET renvoie LOW. RESET est synchronisé en interne. |

| CLK | 19 | Entrée | HORLOGE : Cette broche fournit la synchronisation de base pour le processeur et le contrôleur de bus. Il est asymétrique avec un cycle de travail de 33% pour fournir une synchronisation interne optimisée. |

| Vcc | 40 | HORLOGE : Cette broche est le +5 Volts +/- 10% de l'alimentation fournit. | |

| GND | 1, 20 | TERRE : Ces broches sont la prise de terre. | |

| MN/MX | 33 | Entrée | MINIMUM/MAXIMUM : Ces broches indique que le mode dans lequel le processeur doit fonctionner. |

Les descriptions de fonction de broche suivantes sont pour le mode minimum 8088 (c'est-à-dire MN/MX = Vcc). Seules les fonctions de broche propres au mode minimum sont décrites. toutes les autres fonctions de broche sont telles que décrites ci-dessus :

| Symbole | Broches | Type | Description |

|---|---|---|---|

| IO/M | 28 | Sortie | LIGNE D'ETAT : Cette broche est un mode maximum inversé S2. Il est utilisé pour distinguer un accès mémoire d'un accès d'entrée/sortie. IO/M devient valide dans le T4 précédant un cycle de bus et reste valide jusqu'au T4 final du cycle (I/O = HIGH, M = LOW). IO/M passe à 3 états OFF dans le bus local d'«attente de réception». |

| WR | 29 | Sortie | ÉCRIRE : Cette broche indique que le processeur exécute une mémoire d'écriture ou un cycle d'entrée/sortie d'écriture, en fonction de l'état du signal IO/M. WR est actif pour T2, T3 et Tw de tout cycle d'écriture. Il est actif LOW, et passe à 3 états OFF dans le bus local recevant «Accusé de réception». |

| INTA | 24 | Sortie | INTA : Cette broche est utilisé comme une broche de lecture pour les cycles d'accusé de réception d'interruption. Il est actif LOW pendant T2, T3 et Tw de chaque cycle d'acquittement d'interruption. |

| ALE | 25 | Sortie | ADRESSE DE LOQUET ACTIF : Cette broche indique un signal par le processeur pour verrouiller l'adresse dans un verrou d'adresse. C'est une impulsion HIGH active pendant l'horloge basse de T1 de n'importe quel cycle de bus. Notez que ALE n'est jamais en mode de passage. |

| DT/R | 27 | Sortie | TRANSMISSION/RÉCEPTION DE DONNÉES : Cette broche est nécessaire dans un système minimum désirant utiliser un émetteur-récepteur de bus de données. Il est utilisé pour contrôler la direction du flux de données à travers l'émetteur-récepteur. Logiquement, DT/R est équivalent à S1 dans le mode maximum, et sa minuterie est le même que pour IO/M (T = HIGH, R = LOW). Ce signal passe à 3 états OFF en mode local et reçoit un «Accusé de réception». |

| DEN | 26 | Sortie | DONNÉES ACTIVE : Cette broche est fourni en tant que validation de sortie pour l'émetteur-récepteur de bus de données dans un système minimum utilisant l'émetteur-récepteur. DEN est actif LOW pendant chaque accès mémoire et d'entrée/sortie et pour les cycles INTA. Pour un cycle de lecture ou d'INTA, il est actif du milieu de T2 jusqu'au milieu de T4, alors que pour un cycle d'écriture, il est actif depuis le début de T2 jusqu'au milieu de T4. DEN passe à 3 états OFF pendant le bus local reçoit un «Accusé de réception». |

| HOLD, HLDA | 31, 30 | Entrée/Sortie | HOLD : Ces broches indique qu'un autre maître demande un attente au bus local. Pour être accepté, HOLD doit être actif HIGH. Le processeur recevant la demande d'attente émettra HLDA (HIGH) comme accusé de réception, au milieu d'un cycle d'horloge T4 ou Ti. Simultanément à l'émission de HLDA, le processeur fera passer le bus local et les broches de contrôle. Une fois que HOLD est détecté comme étant LOW, le processeur réduit HLDA, et lorsque le processeur doit exécuter un autre cycle, il entraîne à nouveau le bus local et les broches de contrôle. HOLD et HLDA ont des résistances de pull-up internes. HOLD n'est pas une entrée asynchrone. Une synchronisation externe doit être fournie si le système ne peut pas garantir le temps de mise en oeuvre. |

| SSO | 34 | Sortie | ETAT DE LIGNE : Cette broche est logiquement équivalent à SO dans le mode maximum. La combinaison de SSO, IO/M et DT/R permet au système de décoder complètement l'état actuel du cycle de bus. |

Les descriptions de fonction de broche suivantes concernent le système 8088/8288 en mode maximum (c'est-à-dire, MN/MX = GND). Seules les fonctions de broche propres au mode maximum sont décrites. Toutes les autres fonctions de broche sont décrites ci-dessus.

| Symbole | Broches | Type | Description |

|---|---|---|---|

| S2, S1, S0 | 26 à 28 | Sortie | ETAT : Cette broche est active pendant l'horloge HIGH de T4, T1 et T2 et est renvoyée à l'état passif (1,1,1) pendant T3 ou pendant Tw lorsque READY est HIGH. Cet état est utilisé par le contrôleur de bus 8288 pour générer tous les signaux de contrôle d'accès à la mémoire et aux entrée/sortie. Tout changement de S2, S1 ou S0 pendant T4 est utilisé pour indiquer le début d'un cycle de bus, et le retour à l'état passif dans T3 et Tw est utilisé pour indiquer la fin d'un cycle de bus. Ces signaux passent à 3 états OFF pendant l'attente de confirmation. Pendant le premier cycle d'horloge après que le RESET soit activé, ces signaux sont activés HIGH. Après cette première horloge, ils passent à 3 états OFF. |

| ... | ... | ... | ... |

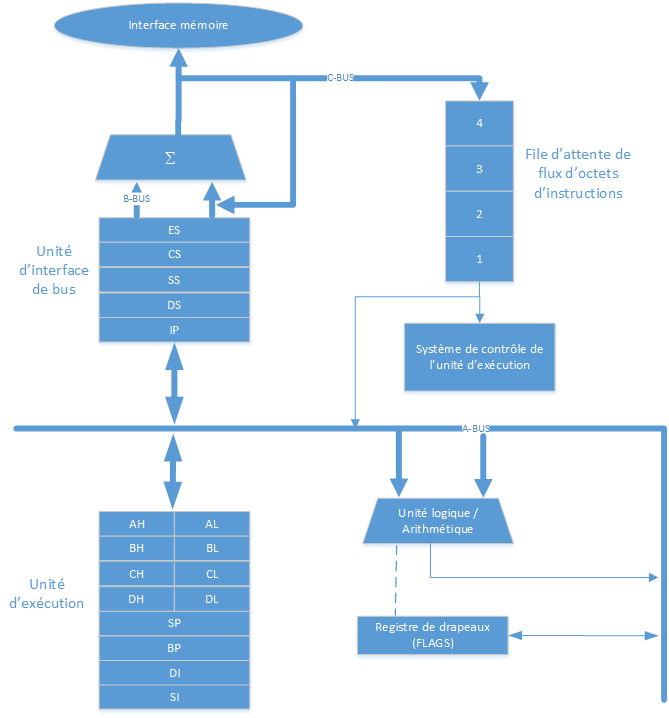

Schéma fonctionnel

Organisation de la mémoire

Le microprocesseur autorise une adresse de 20 bits pour la mémoire localisant l'octet référencé. La mémoire est organisée sous la forme d'un tableau linéaire de 1 million d'octets, adressé de 00000h à FFFFFh. La mémoire est divisée logiquement en code, données, données supplémentaires et segments de pile de 64 Ko maximum chacun. Chaque segment se situant sur des limites de 16 octets.

Toutes les références de mémoire sont faites par rapport aux adresses de base contenues dans les registres de segments appropriés. Les types de segments ont été choisis en fonction des besoins d'adressage des programmes. Le registre de segment à sélectionner est automatiquement choisi en fonction des règles du tableau suivant. Toutes les informations dans un type de segment partagent les mêmes attributs logiques (par exemple, code ou données). En structurant la mémoire en zones relocalisables de caractéristiques similaires et en sélectionnant automatiquement les registres de segments, les programmes sont plus courts, plus rapides et plus structurés.

| Référence mémoire | Segment | Description |

|---|---|---|

| Instructions | Code (CS) | Choisi automatiquement avec tous l;es instructions de la file d'attente. |

| Pile | Pile (SS) | Tous les empilements ou dépilement dans la pile. Les références mémoire relative au registre de base BP sauf les références de données. |

| Donnée locale | Donnée (DS) | Références de données lorsque: par rapport à la pile, la destination de l'opération de chaîne, ou explicité substituée. |

| Donnée externe (global) | Extra (ES) | Destination des opérations de chaîne: Sélection explicite à l'aide d'une substitution de segment. |

Les opérandes de mots (16 bits) peuvent être situés sur des limites d'adresses paires ou impaires. Pour les opérandes d'adresse et de données, l'octet le moins significatif du mot est entreposé dans l'emplacement d'adresse de valeur inférieure et l'octet le plus significatif dans l'emplacement d'adresse supérieur suivant. Le BIU exécutera automatiquement deux cycles d'extraction ou d'écriture pour les opérandes de 16 bits.

Certains emplacements en mémoire sont réservés à des opérations CPU spécifiques. Les emplacements des adresses FFFF0h à FFFFFh sont réservés aux opérations, y compris un saut à la routine d'initialisation initiale du système. Après le RESET, la microprocesseur commencera toujours l'exécution à l'emplacement FFFF0h où le saut doit être localisé. Les emplacements 00000h à 003FFh sont réservés aux opérations d'interruption. Les pointeurs à 4 octets constitués d'une adresse de segment de 16 bits et d'une adresse de décalage de 16 bits dirigent le flux de programme vers l'une des 256 routines de service d'interruption possibles. Les éléments de pointeur sont supposés avoir été entreposés à leurs emplacements respectifs dans la mémoire réservée avant l'apparition des interruptions.

Modes minimum (MN) et maximum (MX)

Les exigences pour la prise en charge des systèmes 8088 minimum et maximum sont suffisamment différentes pour qu'elles ne puissent pas être réalisées efficacement avec 40 broches définies de manière unique. Par conséquent, le 8088 est équipé d'une broche MN/MX définissant la configuration du système. La définition d'un certain sous-ensemble des broches change en fonction de l'état de la broche MN/MX. Lorsque la broche MN/MX est fixée sur GND, le 8088 définit les broches 24 à 31 et 34 en mode maximum. Lorsque la broche MN/MX est attachée à Vcc, le 8088 génère des signaux de contrôle de bus lui-même sur les broches 24 à 31 et 34.

Le mode minimum 8088 peut être utilisé avec un bus multiplexé ou démultiplexé. La configuration du bus multiplexé est compatible avec les périphériques de bus multiplexés MCS-85. Cette configuration fournit à l'utilisateur un système de comptage de puces minimum. Cette architecture fournit la puissance de traitement 8088 sous une forme hautement intégrée.

Le mode démultiplexé nécessite un verrou (pour un adressage de 64 Ko) ou 2 verrous (pour un mégaoctet d'adressage complet). Un 3ième verrou peut être utilisé pour la mise en tampon si le chargement du bus d'adresse l'exige. Un émetteur-récepteur peut également être utilisé si la mise en mémoire tampon du bus de données est requise. Le 8088 fournit DEN et DT/R pour contrôler l'émetteur-récepteur, et ALE pour verrouiller les adresses. Cette configuration du mode minimum fournit à la structure de bus démultiplexée standard un tampon de bus et des exigences de synchronisation de bus relâchées.

Le mode maximum utilise le contrôleur de bus 8288. Le 8288 décode les lignes d'état S0, S1 et S2 et fournit au système tous les signaux de contrôle du bus. Le déplacement du contrôle de bus vers le 8288 fournit une meilleure capacité de courant de source et de puits aux broches de contrôle, et libère les broches 8088 pour les grandes fonctions du système étendues. Le verrouillage matériel, l'état de la file d'attente et 2 interfaces de demande et d'attribution sont fournis par le 8088 en mode maximum. Ces fonctionnalités autorisent les co-processeurs dans les configurations de bus local et de bus distant.

Programmation

| Langage | Description |

|---|---|

| Assembleur 80x86 | Langage Assembleur pour la famille des microprocesseurs 80x86 |

Voir également

Articles - Les géants de l'informatique - Intel