Introduction

|

||||||||||||

La puce ET4000 VLSI Video Graphics Controller de l'entreprise Tseng Labs est conçu pour optimiser les considérations de compromis coût/performance, fournissant une solution rentable pour une génération de contrôleurs d'affichage OEM durant le début des 1990. L'ET4000 est spécifiquement conçu pour les IBM PC/XT/AT, Personal System/Z, et les systèmes compatibles offrant 100% de compatibilité au niveau du registre dans toutes les normes vidéo utilisant les modes VGA, EGA, CGA, MDA et Hercules. Aussi, le BIOS proposé avec la puce ET4000 est compatible avec les fonctionnalités du ET3000.

L'ET4000 est une puce VLSI unique de 1,0 micron se distinguant de la précédente génération de contrôleurs VGA par son haut niveau d'intelligence et de flexibilité dans la gestion des ressources mémoire. Récemment, la technologie de la mémoire est passée de plus en plus large (plus de broches I disponibles à plus profondes, plus de configurations de mémoire I). Cette caractéristique accorde une plus grande importance au contrôleur graphique ASIC (Application Specific Integrated Circuit).

L'entreprise Tseng Labs a créé un tout nouveau approche pour l'ET4000, initiant une nouvelle génération de techniques de conception, en particulier en ce qui concerne les capacités de gestion des ressources mémoire. La puce ET4000 possède plusieurs blocs de mémoire cache, plusieurs blocs de FIFO, une unité de gestion de la mémoire (MCUI) et un contrôleur SPC (System Priority Controller). Ces capacités supplémentaires se traduisent par des exigences de mémoire minimales et des performances système supérieures.

Dans une intégration du contrôleur d'affichage VGA, seulement 2 périphériques de mémoire de 1 Mo sont nécessaires pour maintenir des performances VGA comparables. Des puces de mémoire plus rapides ou supplémentaires installées avec l'ET4000 fourniront une meilleure performance (jusqu'à 17 fois celle du VGA) et n'atteindront aucun état d'attente pendant les accès en écriture en mémoire.

Un autre aspect des fonctionnalités de gestion des ressources mémoire de la puce ET4000 est sa capacité à être reconfigurée pour la quantité de mémoire utilisable sur la carte vidéo. Par exemple, dans l'intégration maximale de la mémoire, si une mémoire défectueuse est détectée pendant une procédure de diagnostic, il est possible de reconfigurer la puce ET4000 avec une mémoire vidéo minimale, bien qu'une perte de performance peut être constaté.

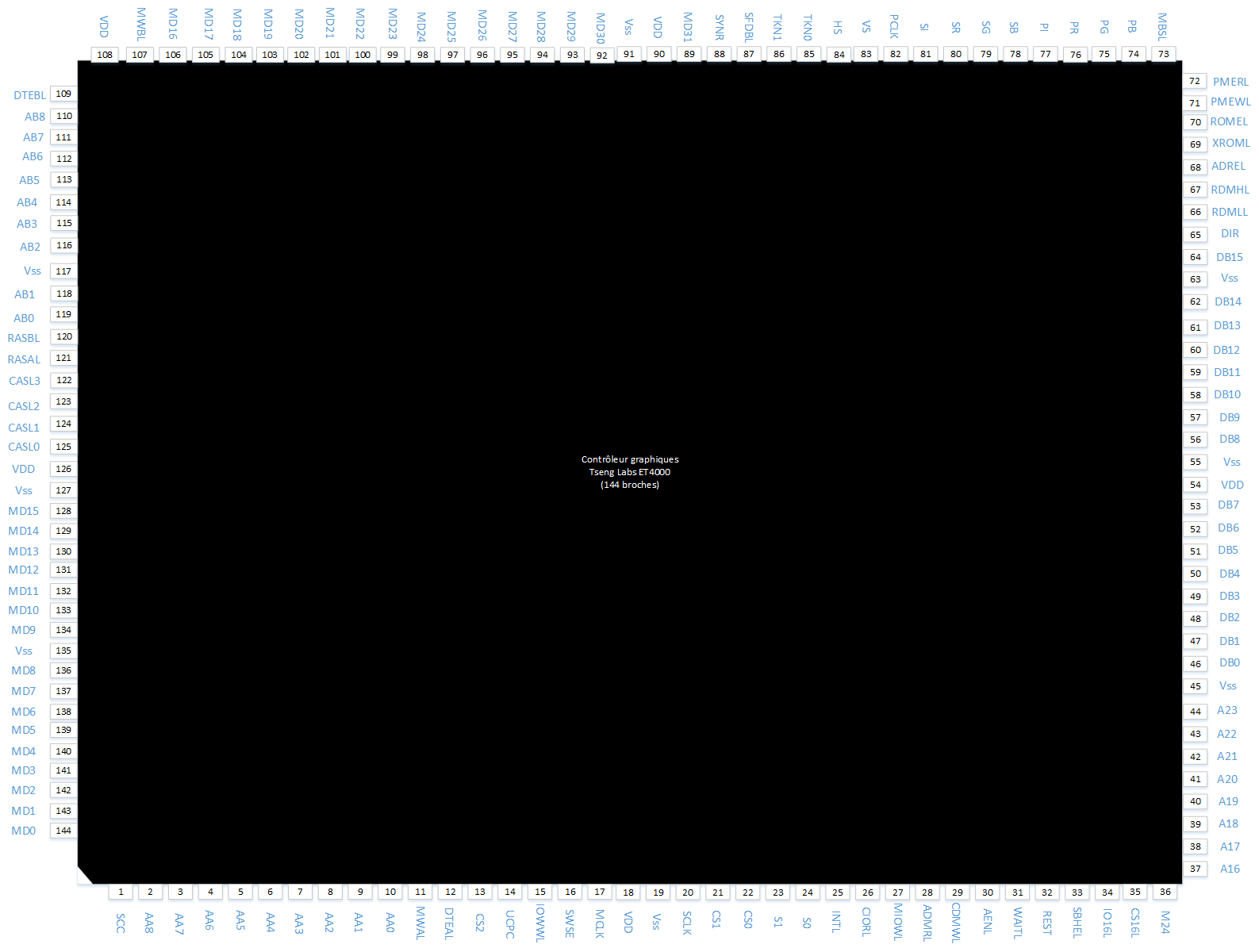

La puce ET4000 est emballé dans une configuration PFP (Module plats en plastique) de 144 broches (ET4000-144) ou 160 broches (ET4000-160).

Interface d'entrée

Le processeur hôte contient les spécifications suivantes :

- Bus de données : Mémoire 8 ou 16 bits et bus d'entrée/sortie via le registre de configuration système ET4000.

- Adresse : Adresse linéaire 20 bits et 4 bits d'adresse de segment.

- Contrôle de bus : Interface de compatibilité PC/AT et PS/2 MCA défini par la broche d'entrée UCPC de l'ET4000.

Interface de sortie

- Moniteur : Entrelacé ou non-entrelacé V-SYNC et H-SYNC avec contrôle de polarité. Palettes 8 bits : SI SR SG SB PI PR PG PB

- Recherche de DAC externe : Horloge de pixel, clignotement, et contrôle de décodage d'entrée/sortie DAC externe.

Gestion des ressources (mémoire)

- Contrôleur de données graphiques : Fonctions de rotation, de masquage et de logique de données compatible avec VGA.

- Cache : LRU (Less Recently Used) et transfert de bloc.

- FIFO : Monte à 2 FIFO pour afficher les données de pixel.

- MCU (Memory Control Unit) : Type de mémoire : 1 Mo (256 Ko x 4) DRAM ou VRAM; 256 Ko (64 Ko x 4) DRAM. Taille de mémoire : VRAM : 8 à un accès aléatoire de 16 bits et 8 à l'accès série 16 bits; DRAM : 8 à un accès aléatoire de 32 bits

- Synchronisation de la mémoire : Minuterie RAS/CAS programmable dans les termes d'une horloge système (indépendant de l'horloge d'affichage); programmable via le registre RCONF de l'ET4000.

- Contrôleur de priorité système (SPC) : SPC intelligent pour résoudre les demandes de ressources multiprocesseurs et ET4000 pour optimiser l'utilisation des ressources MCU.

- Contrôleur CRT : Horizontal : Active l'affichage programmable 8 bits, le clignotement et le H-SYNC. Vertical : Compteur de ligne programmable en 11 bits pour l'activation de l'affichage, le clignotement, la séparation de l'écran et le V-SYNC.

- Contrôleur d'affichage d'adresse : Générateur d'adresse linéaire : Adresse linéaire 18 bits avec une adresse de début programmable; un déplacement d'adresse de ligne. Générateur d'adresse de ligne : Adresse en 5 bits de balayage de lignes fournissant jusqu'à 32 lignes de hauteur par caractères. La position du curseur est en 18 bits : 5 bits pour le début du contrôle de curseur et 5 bits pour la fin du contrôle de curseur.

- Contrôleur d'attribut : Mode texte : Supporte jusqu'à 2 ensembles de 256 caractères; Décodage d'attribut texte compatible à IBM; Soulignement/clignotement du curseur compatible à IBM; Décodage du soulignement compatible avec AT&T (dans le mode texte couleur); Largeur de la police de caractères : Largeur de police de caractères texte : 8, 9, 10, 12 ou 16 pixels. Graphiques : Plage graphiques, octet/mot linéaire (paquet de pixel), Format graphiques couleur CGA et monochrome; Couleur LUT (Look-Up Table) compatible VGA.

- Interface de synchronisation : sélectionne jusqu'à 8 MCLK (horloge de pixel): 65 MHz (graphiques), 56 MHz (texte); horloge système, 40 MHz.

Format d'affichage de données

- Graphique par plage, octet linéaire, mot linéaire format texte compatible VGA allant jusqu'à des caractères Unicode 16 bits

- Compatibilité d'affichage : Résolution : jusqu'à 1024 x 768 pixels en 256 couleurs entrelacé ou non-entrelacé dans le mode graphique. Fréquence d'horloge des pixels : mode graphique en 65 Mhz; mode texte en 56 Mhz.

Compatibilité

- Niveau de registres : CGA/MDA/HERC/EGA/VGA

- Niveau d'affichage : IBM 8514A

- Moniteur : IBM 8503, 8512, 8513, 8514, 5154, 5153, 5151, MultiSync de NEC, MultiSync Plus, XL et les autres moniteurs avec une résolution pouvant allant jusqu'à 1024 x 1024 pixels.

Caractéristiques

- Fournir une simple alimentation de +5V.

- Compatible avec la IBM Video Graphics Array (VGA), Enhanced Graphics Adapter (EGA), CGA/MDA (6845) et une compatibilité au niveau des registres de AT&T/Olivetti.

- Performances brutes jusqu'à 17 fois la vitesse de la génération précédente ET3000 lorsque les 4 VRAM sont utilisés.

- Toute la mémoire d'affichage peut être lu ou écrite avec un délai d'attente minimum (WAIT states) et est pleinement programmable via un bus de données 8 ou 16 bits.

- Tous les registres internes peuvent lu ou écrit et son pleinement programmable via un bus de données 8 ou 16 bits.

- Modification de la mémoire de l'affichage jusqu'à 64 bits en plage de mode graphique.

- Fonction de comparaison des couleurs jusqu'à 64 bits, permettant une comparaison pixel à couleur à l'échelle de l'octet facilitant les opérations de remplissage de zone.

- Registre d'entrée/sortie de traduction en lecture et en écriture.

- Balayage d'affichage entrelacé ou non entrelacé.

- Bit-masquage de données de CPU, sélectionnable par logiciel, permettant la manipulation de la mémoire d'affichage spécifique aux pixels.

- ...

Sous-modèles

Voici la liste des sous-modèles dérivés de la puce ET4000 :

- ET4000AX : L'ET4000AX était une avancée majeure par rapport à l'ensemble de puce ET3000 SVGA de Tseng Labs, avec un nouveau contrôleur d'interface hôte 16 bits avec des capacités de mise en cache et FIFO profondes, et une interface mémoire à largeur variable avec prise en charge de jusqu'à 1 Mo de mémoire avec une largeur de bus de données de mémoire DRAM à 16 bits ou à 32 bits. Les tampons FIFO et les fonctions de cache ont eu pour effet d'améliorer considérablement le débit de l'interface hôte, et donc d'offrir des performances de redessinage sensiblement améliorées par rapport à l'ET3000 et à la plupart de ses concurrentes. Le contrôleur d'interface offre également un support pour le bus MCA d'IBM, en plus d'un bus ISA 8 ou 16 bits. L'ET4000AX peut également prendre en charge la nouvelle norme de bus local VESA avec une logique externe supplémentaire, bien qu'avec une largeur de bus hôte de 16 bits. Ni l'ET4000AX ni les membres de sa famille lui ayant succédé n'ont proposé un RAMDAC intégré, ce qui a ultérieurement entravé la compétitivité coût/performance de la ligne. La puce fut proposé avec la carte Orchid Prodesigner IIs.

- ET4000/W32 : L'accélération matérielle via un BitBLT matériel dédié et un sprite de curseur matériel a été introduite dans l'ET4000/W32. Le W32 offre un support de bus local amélioré avec une performance d'interface hôte encore améliorée, mais au moment où les accélérateurs PCI Windows sont devenus monnaie courante, le débit élevé de l'hôte n'était plus une caractéristique distinctive. Néanmoins, en tant qu'accélérateur Windows à prix moyen, le W32 s'est comparé avantageusement aux puces S3 et ATI de milieu de gamme concurrentes. Configuré avec une DRAM désynchronisé 32 bits EDO/FPM (70 ns), le W32 pouvait supporter une vitesse de transfert de ~56 Mo/s. La puce fut proposé avec la carte Diamond Stealth 32 VLB.

- ET4000/W32i : La révision /W32i comportait un bus mémoire entrelacé de 32 bits (avec 2 Mo de mémoire) pour améliorer le débit de la mémoire. Il prend en charge un maximum de 4 Mo de mémoire vidéo, bien que la plupart des cartes comportant la puce offrent généralement une expansion maximale de 2 Mo ou moins.

- ET4000/W32p : Le sous-modèle W32p offrait un support pour le bus PCI, bien que des révisions antérieures de cette puce (antérieures à la révision D) posaient des problèmes de conception entraînant un fonctionnement sous-optimal ou problématique dans les intégrations PCI, même si les intégrations VLB n'étaient pas affectées. La puce fut proposé avec la carte Integral Technologies I4596 PCI.

Schéma des broches

Voici le schéma des broches de la puce ET4000 de l'entreprise Tseng Labs :

Voir également

Index des entreprises - Tseng Laboratories

Langage de programmation - Assembleur 80x86 - Affichage - Carte vidéo «Tseng Labs ET3000/ET4000»