Introduction

L'ordinateur IBM Personal Computer XT, alias PC XT, est une version du IBM PC avec un disque dur d'inclus. Il fut réalisé par IBM avec le numéro de modèle 5160 en 1983 et il est donc le successeur du modèle PC modèle 5150 (aussi nommé le PC original). Les caractéristiques sont assez proches du IBM PC original avec toutefois la notion qu'un disque dur peut maintenant être inclus en standard dans un ordinateur. De plus, il était possible de démarrer directement à partir du disque dur et non pas à partir d'une disquette. Le PC XT est perçu comme le successeur du IBM PC original et le prédécesseur du PC/AT. Le nom XT provient de l'anglicisme eXtended Technology.

L'ordinateur personnel IBM XT de base se compose d'une unité centrale et d'un clavier. L'unité centrale dispose d'un unité de disque fixe de 10 Mo ou 20 Mo, d'un unité de disquette double face, d'un adaptateur de communication désynchronisé, de 128 Ko de mémoire et de cinq connecteurs d'extension. Le clavier, étant ce que vous utilisez pour envoyer des données à votre système, se fixe à l'unité centrale avec un câble spiralé de 2 mètres (6 pieds). Le clavier se compose de trois sections principales : la zone de la machine à écrire, le pavé numérique et les touches de fonction. Vous pouvez ajouter diverses options à votre système : un écran, une imprimante, une unité d'extension, un unité de disque fixe, de la mémoire,...

L'ordinateur personnel IBM Personal Computer XT est conçu pour être utilisé avec des moniteurs ou des téléviseurs conformes aux normes RS 170 du NTSC (National Television System Committee) ou de l'EIA (Electronics Industry Association). Par conséquent, si votre périphérique ne répond pas à ces normes, il peut ne pas fonctionner correctement. Plusieurs imprimantes sont disponibles pour l'impression ou la copie papier de vos fichiers de données. L'imprimante IBM Graphics Printer et l'imprimante IBM Color Printer fournissent une impression bidirectionnelle en plusieurs tailles de caractères sur des formulaires en une ou plusieurs parties. Une imprimante compacte est également disponible à un prix très attractif. L'unité d'extension offre de l'espace pour des options supplémentaires à connecter à votre ordinateur personnel IBM Personal Computer XT. L'unité d'extension est équipée d'un unité de disque fixe de 10 Mo et, après installation, contient deux unités de disque dur de 10 Mo et six fentes d'extension disponibles.

Fiche technique

Voici les caractéristiques du PC XT d'«IBM» :

| Spécification | Description |

|---|---|

| Fabricant | IBM |

| Année de fabrication | Mars 1983 à avril 1987 |

| Modèle | PC XT |

| Numéro de modèle | 5160 |

| Microprocesseur | Intel 8088, cadencé à 4,77 Mhz |

| Coprocesseur | Socket pour un coprocesseur mathématique 8087, coprocesseur Intel 8087 en option |

| Mémoire vive installée | 128 Ko à 640 Ko |

| Ensemble de puces | 8237-5, 8259A, 8254-2, 8253-5 |

| Média | Une unité de disquette 5,25" ou 3,5" Disque dur de 10 Mo ou 20 Mo |

| Système d'exploitation | PC DOS 2.0 à PC DOS 3.20, PC/IX, SCO Xenix et Minix |

Liste de sous-modèles

| Modèles | Microprocesseur | Mémoire | Système d'exploitation | Année |

|---|---|---|---|---|

| PC XT FD | Intel 8088, 4,77 Mhz | 256 Ko | DOS 2.1 | 1983 à 1987 |

| PC XT DD | Intel 8088, 4,77 Mhz | 256 Ko | DOS 2.11 | 1983 à 1987 |

| PC XT SDD | Intel 8088, 4,77 Mhz | 640 Ko | DOS 2.11 | 1983 à 1987 |

| PC XT SFD | Intel 8088, 4,77 Mhz | 640 Ko | DOS 2.1 | 1983 à 1987 |

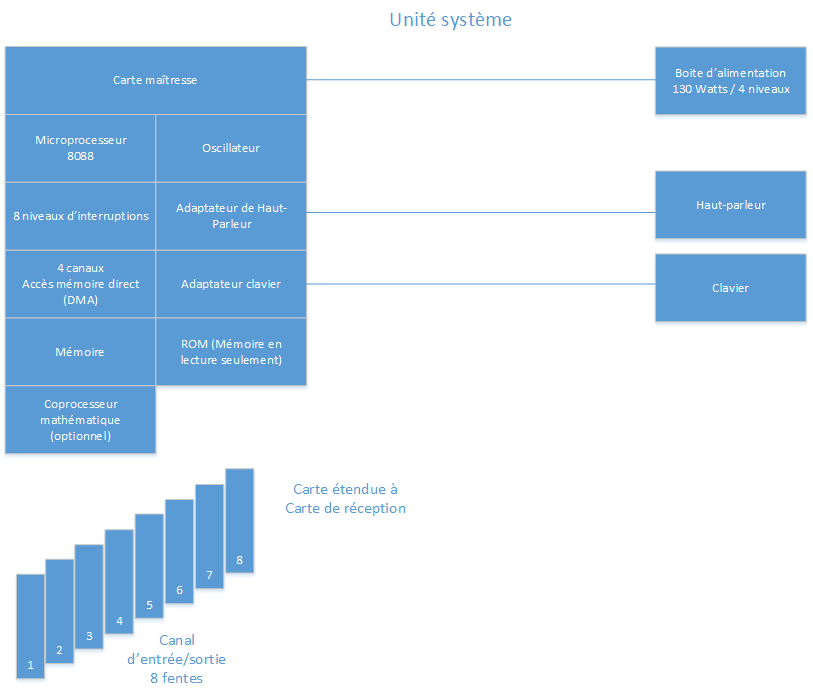

Diagramme de bloc système

Unité système

Le composant principal de votre ordinateur personnel IBM Personal Computer XT est l'unité centrale. Il accomplit toutes les opérations de traitement et de contrôle de votre système via un ensemble d'instructions appelé programme. L'IBM Personal Computer XT est livré avec un programme en langage de programmation, IBM BASIC, déjà installé et de nombreux programmes sont écrits dans ce langage de programmation. Cependant, vous pouvez également écrire des programmes pour votre ordinateur personnel IBM Personal Computer XT dans plusieurs autres langages de programmation pris en charge par IBM. L'unité centrale entrepose les données sur le lecteur de disque dur ou l'unité de disquette à l'aide d'un système d'exploitation tel que le système d'exploitation de disque IBM (DOS). Le IBM DOS permet à l'unité centrale d'entreposer et de récupérer des données à partir de l'unité de disque dur ou de l'unité de disquette.

Carte maîtresse

La carte maîtresse se place horizontalement dans la base de l'unité centrale du Personal Computer XT et mesure environ 215 mm sur 304 mm (8-1/2" x 12"). Il s'agit d'une conception multicouche, à un seul canal par canal, avec un plan de masse et internes fournis. L'alimentation CC (courant continue) envoie un signal provenant de l'alimentation entrant dans la carte via 2 connecteurs à 6 broches. D'autres connecteurs sur la carte servent à attacher le clavier et le haut-parleur. Huit fente d'extension de cartes à 62 broches (ISA) sont également montés sur la carte. Le canal d'entrée/sortie est transporté entre ces 8 emplacements d'entrée/sortie. La fente d'extension J8 est légèrement différente des autres en ce sens que toute carte placée dans celle-ci doit répondre avec un signal «carte sélectionnée» chaque fois que la carte est sélectionnée.

Un commutateur DIP (Dual In-line Package) (soit un ensemble de 8 commutateurs) est monté sur la carte et peut être lu sous le contrôle du programme. Le commutateur DIP fournit aux programmes système des informations sur les options installées, le volume d'entreposage de la carte maîtresse, le type d'adaptateur installé, si le coprocesseur est installé ou non, les modes de fonctionnement souhaités lors de la mise sous tension (affichage en couleur ou en noir et blanc, et une résolution de 40 ou 80 caractères par lignes), et le nombre de lecteurs de disquette attachés.

La carte maîtresse contient les circuits d'adaptateur pour connecter l'interface série au clavier. Ces circuits génèrent une interruption vers le microprocesseur lorsqu'un code de balayage complet est reçu. L'interface peut demander l'exécution d'un test de diagnostic sur le clavier.

La carte maîtresse comprend 5 zones fonctionnelles : le sous-système de processeur et ses éléments de support, le sous-système ROM, le sous-système de lecture/écriture (R/W), les adaptateurs d'entrée/sortie intégrés et le canal d'entrée/sortie.

Microprocesseur

Le coeur de la carte maîtresse est le microprocesseur Intel 8088. Il s'agit d'une version de bus externe 8 bits du microprocesseur Intel 8086 16 bits, compatible avec le 8086. Ainsi, le 8088 prend en charge les opérations 16 bits, notamment les multiplications et les divisions, et 20 bits d'adressage 1 Mo de espace d'adressage. Il fonctionne également en mode maximum, de sorte qu'un coprocesseur peut être ajouté en tant que caractéristique. Le microprocesseur est cadencé à 4,77 MHz. Cette fréquence est dérivée d'un cristal de 14,31818 MHz, dont la fréquence est divisée par 3 pour l'horloge du microprocesseur, et divisée par 4 pour obtenir le signal requis de 3,58 MHz pour les téléviseurs couleur.

Cadencé à la fréquence d'horloge de 4,77 MHz, les cycles de bus du 8088 correspondent à 4 horloges de 210 nanosecondes (ns) chacune, soit 840ns au total. Certains cycles d'entrée/sortie prennent 5 cycles d'horloges de 210ns ou 1,05 microsecondes.

Minuteries système

Trois temporisateurs/compteurs programmables sont utilisés par le système comme suit : le canal 0 est utilisé comme temporisateur à usage général fournissant une base de temps constante pour la mise en oeuvre d'une horloge horaire ; le canal 1 est utilisé pour chronométrer et demander des cycles de rafraîchissement du canal DMA ; et le canal 2 est utilisé pour prendre en charge la génération de tonalité pour le haut-parleur audio. Chaque canal a une résolution temporelle minimale de 1.05-μs.

Interruptions système

Sur les huit niveaux d'interruption prioritaires, six sont acheminés par bus vers les connecteurs d'extension du système pour être utilisés par les cartes de fonction. Deux niveaux sont utilisés sur la carte système. Le niveau 0, la priorité la plus élevée, est attaché au canal 0 du temporisateur/compteur et fournit une interruption périodique pour l'horloge horaire. Le niveau 1 est relié aux circuits adaptateurs du clavier et reçoit une interruption pour chaque code de balayage envoyé par le clavier. L'interruption non masquable (NMI) du 8088 est utilisée pour signaler les erreurs de parité mémoire. Le tableau suivant contient la liste des interruptions système :

| Numéro | Utilisation |

|---|---|

| NMI | Parité8087 |

| 0 | Minuterie |

| 1 | Clavier |

| 2 | Réservé |

| 3 | Communications désynchronisé (Alternative) SDLC Communications BSC Communications Unité d'allocation (Primaire) |

| 4 | Communications désynchronisé (Primaire) Communications SDLC Communications BSC |

| 5 | Disque dur |

| 6 | Disquette |

| 7 | Imprimante Unité d'allocation (Alternative) |

ROM

La carte système prend en charge à la fois la mémoire en lecture seulement (ROM) et la mémoire en lecture/écriture (R/W). Il a de la place pour 64 Ko par 8 de ROM ou de mémoire morte programmable effaçable (EPROM). Deux prises de module sont fournies, chacune pouvant accepter un appareil 32 Ko ou 8 Ko. Un socket a 32 Ko par 8 de ROM, l'autre 8 Ko par 8 octets. Cette ROM contient l'autotest à la mise sous tension, les pilotes d'entrées/sorties, les motifs de points pour 128 caractères en mode graphique et un chargeur d'amorçage de disquette. La ROM est conditionnée en modules à 28 broches et a un temps d'accès et un temps de cycle de 250 ns chacun.

RAM

La carte système dispose également de 128 Ko par 9 à 256 Ko par 9 de mémoire en lecture/écriture (R/W). Un système minimum aurait 128 Ko de mémoire, avec des sockets de module pour 128 Ko supplémentaires. Une mémoire supérieure au maximum de 256 Ko de la carte système est obtenue en ajoutant des cartes mémoire dans les connecteurs d'extension. La mémoire est constituée de puces dynamiques 64 Ko par 1 avec un temps d'accès de 200 ns et un temps de cycle de 345 ns. Toute la mémoire en lecture/écriture (R/W) est vérifiée par parité.

DMA

Le microprocesseur est pris en charge par un ensemble de dispositifs de prise en charge haute fonction fournissant quatre canaux d'accès direct à la mémoire (DMA) 20 bits, trois canaux temporisateur/compteur 16 bits et huit niveaux d'interruption prioritaires. Trois des quatre canaux DMA sont disponibles sur le bus d'entrée/sortie et prennent en charge les transferts de données à grande vitesse entre les périphériques d'entrée/sortie et la mémoire sans intervention du microprocesseur. Le quatrième canal DMA est programmé pour rafraîchir la mémoire dynamique du système. Ceci est réalisé en programmant un canal du dispositif de minuterie/compteur pour demander périodiquement un transfert DMA fictif. Cette action crée un cycle de lecture de mémoire, étant disponible pour actualiser la mémoire dynamique à la fois sur la carte système et dans les connecteurs d'extension système. Tous les transferts de données DMA, à l'exception du canal de rafraîchissement, prennent cinq horloges de microprocesseur de 210-ns, ou 1,05-μs si la ligne "prêt" du microprocesseur n'est pas désactivée. Les cycles de rafraîchissement DMA prennent quatre horloges ou 840-ns.

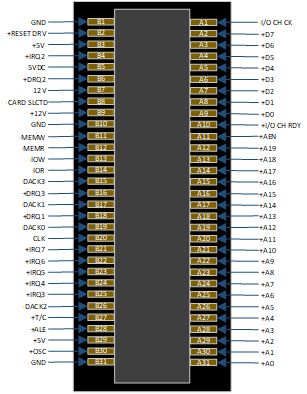

Canal d'entrée/sortie

Le canal d'entrée/sortie est une extension du bus du microprocesseur 8088. Il est cependant démultiplexé, realimenté et amélioré par l'ajout d'interruptions et de fonctions d'accès direct à la mémoire (DMA). Le canal d'entrée/sortie contient un bus de données bidirectionnel à 8 bits, 20 lignes d'adresse, 6 niveaux d'interruption, des lignes de contrôle pour la mémoire et des entrée/sortie en lecture ou écriture, des lignes d'horloge et de synchronisation, 3 canaux de lignes de contrôle DMA, un rafraîchissement de la mémoire -des lignes de contrôle de synchronisation, une ligne de «contrôle de canal», et l'alimentation et la terre pour les adaptateurs. Quatre niveaux de tension sont fournis pour les cartes d'entrées/sorties : +5 Vdc, -5 Vdc, + 12 Vdc et -12 Vdc. Ces fonctions sont fournies dans un connecteur à 62 broches avec un espacement des tab de carte de 100 mil. Une ligne « prêt » est disponible sur le canal d'entrée/sortie pour permettre le fonctionnement avec des périphériques d'entrée/sortie lents ou de mémoire. Si la ligne "prêt" du canal n'est pas activée par un périphérique adressé, tous les cycles de lecture et d'écriture de la mémoire générée par le microprocesseur prennent quatre cycles d'horloge de 210 ns ou 840 ns/octet. Tous les cycles de lecture et d'écriture d'entrée/sortie générés par microprocesseur nécessitent cinq horloges pour un temps de cycle de 1,05-/Ls/octet. Tous les transferts DMA nécessitent cinq horloges pour un temps de cycle de 1,05-μs/octet. Les cycles de rafraîchissement se produisent une fois toutes les 72 horloges (environ 15-μs) et nécessitent quatre horloges ou environ 7% de la bande passante du bus. Les périphériques d'entrée/sortie sont adressés à l'aide de l'espace d'adressage cartographié des entrées/sorties. Le canal est conçu de manière à ce que 768 adresses de périphérique d'entrées/sorties soient disponibles pour les cartes de canal d'entrées/sorties. Une ligne de « contrôle de canal » existe pour signaler les conditions d'erreur au microprocesseur. L'activation de cette ligne entraîne une interruption non masquable (NMI) vers le microprocesseur 8088. Les options d'extension de mémoire utilisent cette ligne pour signaler les erreurs de parité. Le canal d'entrée/sortie est réputé pour fournir un lecteur suffisant pour alimenter les huit emplacements d'extension (J1 à J8), en supposant deux charges Schottky (LS) à faible consommation par emplacement. Les adaptateurs d'entrées/sorties IBM n'utilisent généralement qu'une seule charge. Les exigences de synchronisation sur la fente 18 sont beaucoup plus strictes que celles sur les fentes J1 à J7. La fente J8 exige également que la carte fournisse un signal désignant le moment où la carte est sélectionnée.

| Signal | Entrée/sortie | Description |

|---|---|---|

| A0 à A19 | Sortie | Bits d'adresse 0 à 19 : Ces lignes sont utilisées pour adresser la mémoire et les périphériques d'entrée/sortie au sein du système. Les 20 lignes d'adresse permettent l'accès jusqu'à 1 Mégaoctets de mémoire. A0 est le bit le moins significatif (LSB) et A19 est le bit le plus significatif (MSB). Ces lignes sont générées soit par le microprocesseur, soit par le contrôleur DMA. Ils sont actifs haut. |

| AEN | Sortie | Address Enable : Cette ligne est utilisée pour déporter le microprocesseur et d'autres périphériques du canal d'entrée/sortie afin de permettre les transferts DMA. Lorsque cette ligne est active (haute), le contrôleur DMA contrôle le bus d'adresse, le bus de données, les lignes de commande de lecture (mémoire et entrée/sortie) et les lignes de commande d'écriture (mémoire et entrée/sortie). |

| ALE | Sortie | Address Latch Enable : Cette ligne est fournie par le contrôleur de bus 8288 et est utilisée sur la carte système pour verrouiller les adresses valides du microprocesseur. Il est disponible pour le canal d'entrée/sortie en tant qu'indicateur d'une adresse de microprocesseur valide (lorsqu'il est utilisé avec AEN). Les adresses du microprocesseur sont verrouillées avec le front descendant de l'ALE. |

| -CARD SLCTD | Entrée | -Card Selected : Cette ligne est activée par les cartes dans la fente d'extension J8. Il signale à la carte système que la carte a été sélectionnée et que les pilotes appropriés sur la carte système doivent être dirigés vers la lecture ou l'écriture sur le connecteur d'extension J8. Les connecteurs J1 à J8 sont liés ensemble à cette broche, mais la carte système n'utilise pas leur signal. Cette ligne doit être entraînée par un dispositif à collecteur ouvert. |

| CLK | Sortie | Horloge système : c'est une division par 3 de l'oscillateur et a une période de 210 ns (4,77 MHz). L'horloge a un rapport cyclique de 33%. |

| D0 à D7 | Entrée/sortie | Bits de données 0 à 7 : ces lignes fournissent les bits de bus de données 0 à 7 pour le microprocesseur, la mémoire et les périphériques d'entrée/sortie. D0 est le LSB et D7 est le MSB. Ces lignes sont actives haut. |

| -DACK0 à -DACK3 | Sortie | -DMA Acknowledge 0 à 3 : Ces lignes sont utilisées pour accuser réception des requêtes DMA (DRQI-DRQ3) et rafraîchir la mémoire dynamique du système (-DACK0). Ils sont actifs bas. |

| DRQ1 à DRQ3 | Entrée | Requête DMA 1 à 3 : ces lignes sont des requêtes de canal désynchronisés utilisées par les périphériques pour obtenir le service DMA. Ils sont hiérarchisés, DRQ3 étant le plus bas et DRQ1 étant le plus élevé. Une requête est générée en amenant une ligne DRQ à un niveau actif (élevé). Une ligne DRQ doit être maintenue à l'état haut jusqu'à ce que la ligne DACK correspondante devienne active. |

| -I/O CH CK | Entrée | -Contrôle du canal d'entrée/sortie : cette ligne fournit au microprocesseur des informations de parité (erreur) sur la mémoire ou les périphériques du canal d'entrée/sortie. Lorsque ce signal est actif bas, une erreur de parité est indiquée. |

| I/O CHRDY | Entrée | Canal d'entrée/sortie prêt : cette ligne, normalement haute (prête), est tirée vers le bas (pas prête) par une mémoire ou un périphérique d'entrée/sortie pour allonger les cycles d'entrée/sortie ou de mémoire. Il permet aux périphériques plus lents de se connecter au canal d'entrée/sortie avec un minimum de difficulté. Tout périphérique lent utilisant cette ligne devrait l'abaisser immédiatement après avoir détecté une adresse valide et une commande de lecture ou d'écriture. Cette ligne ne doit jamais être maintenue basse plus de 10 cycles d'horloge. Les cycles machine (entrée/sortie ou mémoire) sont prolongés d'un nombre entier de cycles d'horloge (210 ns). |

| -IOR | Sortie | -Commande de lecture d'entrée/sortie : cette ligne de commande indique à un périphérique d'E/S de conduire ses données sur le bus de données. Il peut être piloté par le microprocesseur ou le contrôleur DMA. Ce signal est actif bas. |

| -LOW | Sortie | -Commande d'écriture d'entrée/sortie : cette ligne de commande indique à un périphérique d'entrée/sortie de lire les données sur le bus de données. Il peut être piloté par le microprocesseur ou le contrôleur DMA. Ce signal est actif bas. |

| IRQ2 à IRQ7 | Entrée | Requête d'interruption 2 à 7 : Ces lignes sont utilisées pour signaler au microprocesseur qu'un périphérique d'entrée/sortie nécessite une attention. Ils sont hiérarchisés avec IRQ2 comme priorité la plus élevée et IRQ7 comme la plus basse. Une demande d'interruption est générée en élevant une ligne IRQ (de bas en haut) et en la maintenant haute jusqu'à ce qu'elle soit acquittée par le microprocesseur (programme de service d'interruption). |

| -MEMR | Sortie | -Commande de lecture de mémoire : cette ligne de commande indique à la mémoire de conduire ses données sur le bus de données. Il peut être piloté par le microprocesseur ou le contrôleur DMA. Ce signal est actif bas. |

| -MEMW | Sortie | -Memory Write Command : cette ligne de commande indique à la mémoire d'entreposer les données présentes sur le bus de données. Il peut être piloté par le microprocesseur ou le contrôleur DMA. Ce signal est actif bas. |

| OSC | Sortie | Oscillateur : Horloge haute vitesse avec une période de 70 ns (14,31818 MHz). Il a un cycle de service de 50%. |

| RESET DRV | Sortie | Reset Drive : Cette ligne est utilisée pour réinitialiser ou initialiser la logique du système lors de la mise sous tension ou lors d'une panne de tension secteur faible. Ce signal est synchronisé sur le front descendant de CLK et est actif à l'état haut. |

| T/C | Sortie | Nombre de terminaux : cette ligne fournit une impulsion lorsque le nombre de terminaux pour n'importe quel canal DMA est atteint. Ce signal est actif haut. |

Circuit de haut-parleur

L'unité centrale est dotée d'un haut-parleur de 57,15 mm (2-1/4 po). Les circuits de commande et le pilote du haut-parleur se trouvent sur la carte système. Le haut-parleur se connecte via une interface à 2 fils qui se connecte à un connecteur à 3 broches sur la carte système. Le circuit d'entraînement du haut-parleur est capable d'environ 1/2 watt de puissance. Les circuits de commande permettent au haut-parleur d'être piloté de trois manières différentes :

- un bit de registre de commande de programme direct peut être basculé pour générer un train d'impulsions

- la sortie du canal 2 du compteur de minuterie peut être programmée pour générer une forme d'onde vers le haut-parleur

- l'entrée d'horloge du compteur horaire peut être modulée avec un bit de registre d'entrée/sortie commandé par programme.

Les trois méthodes peuvent être exécutées simultanément.

Carte de bits d'entrée/sortie 8255A

La carte de bits d'entrée/sortie 8255A affiche les entrées et les sorties du registre de commande/mode sur la carte système. Sont également affichés les réglages des commutateurs pour la mémoire, l'affichage et le nombre d'unités de disquettes.

Coprocesseur

Le coprocesseur mathématique (8087) permet à l'ordinateur personnel IBM d'effectuer des opérations arithmétiques, logarithmiques et trigonométriques à grande vitesse avec une précision extrême. Le coprocesseur 8087 fonctionne en parallèle avec le microprocesseur. Le fonctionnement en parallèle diminue le temps de fonctionnement en permettant au coprocesseur d'effectuer des calculs mathématiques tandis que le microprocesseur continue d'effectuer d'autres fonctions. Les cinq premiers bits du code d'opération de chaque instruction pour le coprocesseur sont identiques (binaire 110 11). Lorsque le microprocesseur et le coprocesseur voient ce code d'opération, le microprocesseur calcule l'adresse de toutes les variables en mémoire, tandis que le coprocesseur vérifie l'instruction. Le coprocesseur prend l'adresse mémoire du microprocesseur si nécessaire. Pour accéder aux emplacements en mémoire, le coprocesseur prend le bus local du microprocesseur lorsque le microprocesseur termine son instruction en cours. Lorsque le coprocesseur a terminé le transfert mémoire, il renvoie le bus local au microprocesseur. Le coprocesseur mathématique IBM fonctionne avec sept types de données numériques répartis dans les trois classes répertoriées ci-dessous

- Entiers binaires (3 types)

- Entiers décimaux (1 type)

Nombres réels (3 types)

Interface de programmation

Le coprocesseur étend les types de données, les registres et les instructions au microprocesseur. Le coprocesseur possède huit registres de 80 bits, fournissant la capacité équivalente des 40 registres de 16 bits présents dans le microprocesseur. Cet espace de registre permet de conserver des constantes et des résultats temporaires dans des registres pendant les calculs, réduisant ainsi l'accès à la mémoire et améliorant la vitesse ainsi que la disponibilité du bus. L'espace de registre peut être utilisé comme une pile ou comme un ensemble de registres fixes. Lorsqu'il est utilisé comme une pile, seuls les deux éléments supérieurs de la pile sont exploités. La tableau suivant montre des représentations de grands et de petits nombres dans chaque type de données :

| Type de données | Bits | Chiffres significatifs (décimaux) | Intervalle approximative (décimale) |

|---|---|---|---|

| Mot entier (Word Integer) | 16 | 4 | -32 768≤5 X≤5 + 32 767 |

| Entier court (Short Integer) | 32 | 9 | -2x109 ≤ X ≤ + 2x109 |

| Entier long (Long Integer) | 64 | 18 | -9x1018 ≤X≤ + 9x1018 |

| Décimal compacté (Packed Decimal) | 80 | 18 | -99..99≤X≤ + 99...99 (18 chiffres) |

| Réel court (Short Real) | 32 | 6 à 7 | 8,43x1037 ≤|X|≤3,37x1038 |

| Réel long (Long Real) | 64 | 15 à 16 | 4.19x10-307 ≤ |X| ≤ 1.67x10308 |

| Réel temporaire (Temporary Real) | 80 | 19 | 3,4x10-4932 ≤|X| ≤ 1,2x104932 |

Interface matérielle

Le coprocesseur utilise les mêmes composantes de générateur d'horloge et d'interface de bus système que le microprocesseur. Le coprocesseur est câblé directement dans le microprocesseur. Les lignes d'état de file d'attente du microprocesseur (QS0 et QS1) permettent au coprocesseur d'obtenir et de décoder des instructions simultanément avec le microprocesseur. Le signal "busy" du coprocesseur informe le microprocesseur qu'il est en cours d'exécution ; l'instruction WAIT du microprocesseur force le microprocesseur à attendre la fin de l'exécution du coprocesseur (WAIT FOR NOT BUSY). Lorsqu'une instruction incorrecte est envoyée au coprocesseur (par exemple, diviser par 0 ou charger un registre plein), le coprocesseur peut signaler au microprocesseur une interruption. Il y a trois conditions qui désactiveront l'interruption du coprocesseur vers le microprocesseur :

- Les bits d'exception et d'activation d'interruption du mot de contrôle sont mis à 1.

- Bloc-interrupteurs de la carte système 1, interrupteur 2, mis en position Marche.

- Le registre (REG) d'interruption non masquable (NMI) est mis à zéro.

Au moment de la mise sous tension, le REG du NMI est effacé pour désactiver le NMI. Tout programme utilisant la capacité d'interruption du coprocesseur doit garantir que les conditions 2 et 3 ne sont jamais remplies pendant le fonctionnement du logiciel, sinon une Endless WAIT (attente sans fin) se produira. Une Endless WAIT aura sur le microprocesseur une attende de signal "not busy" du coprocesseur tandis que le coprocesseur attend que le microprocesseur interrompe. Parce qu'une erreur de parité mémoire peut également provoquer une interruption de la ligne NMI du microprocesseur, le programme doit vérifier l'état du coprocesseur pour une condition d'exception. Si une condition d'exception de coprocesseur n'est pas trouvée, le contrôle doit être passé au gestionnaire NMI normal. Si une condition d'exception 8087 est trouvée, le programme peut effacer l'exception en exécutant l'instruction FNSAVE ou FNCLEX, et l'exception peut être identifiée et traitée. Le REG du NMI et l'interruption du coprocesseur sont liés à la ligne NMI via la logique d'interruption NMI. Des modifications mineures aux programmes conçus pour être utilisés avec un coprocesseur doivent être apportées avant que les programmes ne soient compatibles avec le coprocesseur IBM Personal Computer Math.

Adresse des ports d'entrée/sortie

Voici la liste des adresses de ports d'entrée/sortie qu'utilise le carte maîtresse pour communiquer avec ses composantes :

| Adresse | Description |

|---|---|

| 0000h à 001Fh | Contrôleur DMA, 8237-5 |

| 0020h à 003Fh | Contrôleur d'interruption, 8259A, maître |

| 0040h à 005Fh | Minuterie, 8254-2 |

| 0060h à 006Fh | PPI 8253-5 |

| 0080h à 009Fh | Registre de page DMA |

| 00A0h à 00AFh | Masque de registres NMI |

| 0200h à 020Fh | Contrôleur de jeux |

| 0201h | Entrée/sortie de jeux |

| 020Ch à 020Dh | Réservé |

| 0278h à 027Fh | Port parallèle d'imprimante 2 |

| 02B0h à 02DFh | Adaptateur alternatif de graphique étendue (EGA) |

| 02E1h | GPIB (Adaptateur 0) |

| 02E2h à 02E4h | Acquisition de données (Adaptateur 0) |

| 02F8h à 02FFh | Port série 2 |

| 0300h à 031Fh | Carte de prototype |

| 0320h à 032Fh | Disque fixe |

| 0348h à 0357h | DCA 3278 |

| 0360h à 0367h | Réseau PC (adresse base) |

| 0368h à 036Fh | Réseau PC (adresse haute) |

| 0378h à 037Fh | Port parallèle d'imprimante 1 |

| 0380h à 038Fh | SDLC, bisynchronisé 2 |

| 0390h à 0393h | Unité d'allocation |

| 03A0h à 03AFh | Bisynchronisé 1 |

| 03B0h à 03BFh | Adaptateur d'affichage monochrome et d'imprimante (MDA) |

| 03C0h à 03CFh | Adaptateur de graphique étendue (EGA) |

| 03D0h à 03DFh | Adaptateur de graphique couleur (CGA) |

| 03F0h à 03F7h | Contrôleur de disquette |

| 03F8h à 03FFh | Port série 1 |

| 06E2h à 06E3h | Acquisition de données (Adaptateur 1) |

| 0790h à 0793h | Unité d'allocation (Adaptateur 1) |

| 0AE2h à 0AE3h | Acquisition de données (Adaptateur 2) |

| 0B90h à 0B93h | Unité d'allocation (Adaptateur 2) |

| 0EE2h à 0EE3h | Acquisition de données (Adaptateur 3) |

| 1390h à 1393h | Unité d'allocation (Adaptateur 3) |

| 22E1h | GPIB (Adaptateur 1) |

| 2390h à 2393h | Unité d'allocation (Adaptateur 4) |

| 42E1h | GPIB (Adaptateur 2) |

| 62E1h | GPIB (Adaptateur 3) |

| 82E1h | GPIB (Adaptateur 4) |

| A2E1h | GPIB (Adaptateur 5) |

| C2E1h | GPIB (Adaptateur 6) |

| E2E1h | GPIB (Adaptateur 7) |

Remarque

- Les adresses de port d'entrée/sortie de 0000h à 00FFh sont réservés pour les ports d'entrée/sortie de la carte maîtresse. Les adresses de 0100h à 03FFh sont disponibles pour les canaux d'entrée/sortie. La carte maîtresse décode jusqu'à 10 bits d'informations d'adresse d'entrée/sortie. Les adresses d'entrée/sortie ne doivent pas être en conflit avec les adresses de port d'entrée/sortie de la carte maîtresse.

Utilisation du BIOS système

Le système d'entrée/sortie de base (BIOS) réside dans la ROM de la carte système et fournit un contrôle au niveau du périphérique pour les principaux périphériques d'entrée/sortie du système. Des modules ROM supplémentaires peuvent être situés sur les adaptateurs en option pour fournir un contrôle au niveau du périphérique pour cet adaptateur en option. Les routines du BIOS permettent au programmeur en langage de programmation assembleur 8086 d'effectuer des opérations d'entrée/sortie de niveau bloc (disque et disquette) ou caractère sans se soucier de l'adresse du périphérique et des caractéristiques de fonctionnement. Les services système, tels que la détermination de l'heure et de la taille de la mémoire, sont fournis par le BIOS.

L'objectif est de fournir une interface opérationnelle au système et de soulager le programmeur des préoccupations concernant les caractéristiques des périphériques matériels. L'interface BIOS isole l'utilisateur du matériel, permettant ainsi d'ajouter de nouveaux périphériques au système, tout en conservant l'interface de niveau BIOS avec le périphérique. De cette manière, les programmes utilisateur deviennent transparents aux modifications et améliorations matérielles. Chaque point d'entrée du BIOS est disponible via sa propre interruption. Les interruptions logicielles, 10 (en hexadécimal) à 1A (en hexadécimal), accèdent chacune à une routine BIOS différente. Par exemple, pour déterminer la quantité de mémoire disponible dans le système :

- INT 12H

invoque la routine BIOS pour déterminer la taille de la mémoire et renvoie la valeur à l'appelant.

Passage de paramètres

Tous les paramètres transmis vers et depuis les routines du BIOS passent par les registres 8088. Le prologue de chaque fonction du BIOS indique les registres utilisés sur l'appel et le retour. Pour l'exemple de taille de mémoire, aucun paramètre n'est passé. La taille de la mémoire, par incréments de 1 Ko, est renvoyée dans le registre AX. Si une fonction BIOS a plusieurs opérations possibles, le registre AH est utilisé en entrée pour indiquer l'opération souhaitée. Par exemple, pour régler l'heure du jour, le code suivant est requis :

Pour lire l'heure de la journée :

Généralement, les routines du BIOS enregistrent tous les registres à l'exception de AX et des drapeaux. Les autres registres ne sont modifiés au retour que s'ils renvoient une valeur à l'appelant. L'utilisation exacte du registre est dans le prologue de chaque fonction du BIOS.

Interruption hexadécimal 1E : Paramètres de la disquette

Ce vecteur pointe vers une région de données contenant les paramètres requis pour le lecteur de disquette. Les routines de mise sous tension initialisent le vecteur pour pointer vers les paramètres contenus dans la routine de disquette ROM. Ces paramètres par défaut représentent les valeurs spécifiées pour tous les unités de disques IBM connectés au système. La modification de ce bloc de paramètres peut être nécessaire pour refléter les spécifications des autres variateurs connectés.

Interruption hexadécimal 1F : Extensions de caractères graphiques

Lors du fonctionnement dans les modes graphiques de l'adaptateur de moniteur couleur/graphique IBM (320x200 ou 640x200), l'interface de caractères de lecture/écriture forme le caractère à partir du point de code ASCII, à l'aide d'un ensemble de motifs de points. Les motifs de points pour les 128 premiers points de code sont contenus dans la ROM. Pour accéder aux 128 seconds points de code, ce vecteur doit être établi pour pointer vers une table de jusqu'à 1 Ko, où chaque point de code est représenté par huit octets d'informations graphiques. A la mise sous tension, ce vecteur est initialisé à 000:0, et il est de la responsabilité de l'utilisateur de modifier ce vecteur si des points de code supplémentaires sont nécessaires.

Interruption hexadécimal 40 - Réservé

Lorsqu'un adaptateur de disque dur IBM est installé, les routines du BIOS utilisent l'interruption hexadécimale 30 pour revectoriser le pointeur de disquette.

Interruption hexadécimal 41 - Paramètres de disque durs

Ce vecteur pointe vers une région de données contenant les paramètres requis pour l'unité de disque dur. Les routines de mise sous tension initialisent le vecteur pour pointer vers les paramètres contenus dans la routine de disque ROM. Ces paramètres par défaut représentent les valeurs spécifiées pour toutes les unités de disque dur IBM connectées au système. La modification de ce bloc de paramètres peut être nécessaire pour refléter les spécifications des autres lecteurs de disques durs connectés.

Autre utilisation de la mémoire en lecture/écriture

Les routines du BIOS d'IBM utilisent 256 octets de mémoire de 400 hexadécimal absolu à 4FF hexadécimal. Les emplacements hexadécimal 400 à 407 contiennent les adresses de base de toutes les cartes RS-232C connectées au système. Les emplacements hexadécimal 408 à 40F contiennent les adresses de base de l'adaptateur d'imprimante. Les emplacements de mémoire hexadécimaux 300 à 3FF sont utilisés comme zone de pile pendant l'initialisation de la mise sous tension et amorcent lorsque le contrôle lui est transmis à la mise sous tension. Si l'utilisateur souhaite la pile dans une zone différente, la zone doit être définie par l'application.

Interruptions réservées aux BASIC et DOS

| Adresse (Hexadécimal) | Interruption (Hexadécimal) | Fonction |

|---|---|---|

| 80 à 83 | 20 | Fin du programme DOS |

| 84 à 87 | 21 | Appel de fonction DOS |

| 88 à 8B | 22 | Adresse de terminaison DOS |

| 8C à 8F | 23 | Adresse de sortie du Ctrl+Break du DOS |

| 90 à 93 | 24 | Vecteur d'erreur fatale DOS |

| 94 à 97 | 25 | Lecture de disque absolue DOS |

| 98 à 9B | 26 | Écriture sur disque absolue DOS |

| 9C à 9F | 27 | Terminer le DOS, réparer dans l'entreposage |

| A0 à FF | 28 à 3F | Réservé au DOS |

| 100 à 17F | 40 à 5F | Réservé |

| 180 à 19F | 60 à 67 | Réservé aux interruptions du logiciel utilisateur |

| 1A0 à 1FF | 68 à 7F | Non utilisé |

| 200 à 217 | 80 à 85 | Réservé par BASIC |

| 218 à 3C3 | 86 à F0 | Utilisé par l'interpréteur BASIC pendant que BASIC est en cours d'exécution |

| 3C4 à 3FF | F1 à FF | Non utilisé |

Liste des interruptions logicielles 8088

| Adresse (hexadécimal) | Numéro d'interruption | Nom | Entré BIOS |

|---|---|---|---|

| 0 à 3 | 0 | Division par zéro | D11 |

| 4 à 7 | 1 | Simple saut | D11 |

| 8 à B | 2 | Non masquable | NMI_INT |

| C à F | 3 | Point d'arrêt | D11 |

| 10 à 13 | 4 | Débordement | D11 |

| 14 à 17 | 5 | Impression de l'écran | PRINT_SCREEN |

| 18 à 1B | 6 | Réservé | D11 |

| 1D à 1F | 7 | Réservé | D11 |

| 20 à 23 | 8 | Heure de la journée | TIMER_INT |

| 24 à 27 | 9 | Clavier | KB_INT |

| 28 à 2B | A | Réservé | D11 |

| 2C à 2F | B | Communications | D11 |

| 30 à 33 | C | Communications | D11 |

| 34 à 37 | D | Disque | D11 |

| 38 à 3B | E | Disquette | DISK INT |

| 3C à 3F | F | Imprimante | D11 |

| 40 à 43 | 10 | Vidéo | VIDEO_IO |

| 44 à 47 | 11 | Vérification de l'équipement | EQUIPMENT |

| 48 à 4B | 12 | Mémoire | MEMORY_SIZE_DETERMINE |

| 4C à 4F | 13 | Disquette/Disque | DISKETTE_IO |

| 50 à 53 | 14 | Communications | RS232_IO |

| 54 à 57 | 15 | Cassette | CASSETTE_IO |

| 58 à 5B | 16 | Clavier | KEYBOARD_IO |

| 5C à 5F | 17 | Imprimante | PRINTER_IOL |

| 60 à 63 | 18 | BASIC résident | F600:0000 |

| 64 à 67 | 19 | Amorçage | BOOT_STRAP |

| 68 à 6B | 1A | Moment de la journée | TIME_OF_DAY |

| 6C à 6F | 1B | Pause clavier | DUMMY RETURN |

| 70 à 73 | 1C | Tic de la minuterie | DUMMY RETURN |

| 74 à 77 | 1D | Initialisation vidéo | VIDEO_PARMS | 78 à 7B | 1E | Paramètres de la disquette | DISK BASE |

| 7C à 7F | 1F | Caractères graphiques vidéo | 0 |

| 100 à 103 | 40 | Zone de sauvegarde du pointeur de disquette pour le disque fixe | |

| 104 à 107 | 41 | Paramètres de disque durs | FD TBL |

| 168 à 16B | 5A | Unité d'allocation | D000:XXXX |

| 16C à 16F | 5B | Utilisé par le programme d'unité d'allocation | |

| 180 à 19F | 60 à 67 | Réservé aux programmes utilisateur |

Interruption hexadécimal 1B - Adresse de rupture de clavier

Ce vecteur pointe vers le code à utiliser lorsque les touches Ctrl+Break sont enfoncées sur le clavier. Le vecteur est invoqué lors de la réponse à l'interruption du clavier et le contrôle doit être renvoyé via une instruction IRET. Les routines de mise sous tension initialisent ce vecteur à une instruction IRET, de sorte que rien ne se produira lorsque les touches Ctrl+Break sont enfoncées à moins que le programme d'application ne définisse une valeur différente. Le contrôle peut être conservé par cette routine, avec les problèmes suivants. La rupture peut s'être produite pendant le traitement de l'interruption, de sorte qu'une ou plusieurs commandes de fin d'interruption doivent être envoyées au contrôleur 8259. De plus, tous les périphériques d'entrée/sortie doivent être réinitialisés au cas où une opération était en cours à ce moment-là.

Interruption hexadécimal 1C - Tic de minuterie

Ce vecteur pointe vers le code à exécuter à chaque impulsion de l'horloge système. Ce vecteur est invoqué lors de la réponse à l'interruption du temporisateur, et le contrôle doit être renvoyé via une instruction IRET. Les routines de mise sous tension initialisent ce vecteur pour pointer vers une instruction IRET, de sorte que rien ne se produira à moins que l'application ne modifie le pointeur. Il est de la responsabilité de l'application de sauvegarder et de restaurer tous les registres étant modifiés.

Interruption hexadécimal 1D - Paramètres vidéo

Ce vecteur pointe vers une région de données contenant les paramètres nécessaires à l'initialisation du 6845 sur la carte vidéo. Notez qu'il existe quatre tableaux distincts et que tous les quatre doivent être reproduits si tous les modes de fonctionnement doivent être pris en charge. Les routines de mise sous tension initialisent ce vecteur pour pointer sur les paramètres contenus dans les routines vidéo ROM.

Emplacements de mémoire réservés

| Adresse (hexadécimal) | Mode | Fonction | |

|---|---|---|---|

| 400 à 48F | ROM BIOS | BIOS en ROM | |

| 490 à 4EF | Réserve | ||

| 4F0 à 4FF | Réservé en Intra-ApplicationEspace de communication pour toute application | ||

| 500 à 5FF | Réservé pour DOS et BASIC | ||

| 500 | DOS Drapeau d'entreposage de l'état d'impression de l'écran : | ||

| Valeur | Description | ||

| 0 | Opération d'impression d'écran non active ou opération d'écran réussie | ||

| 1 | Impression écran en cours | ||

| 255 | Erreur rencontrée lors du fonctionnement de l'impression de l'écran | ||

| 504 | DOS | Octet d'état du mode d'unité de disque unique | |

| 510 à 511 | BASIC | Entreposage d'adresses de segment de BASIC | |

| 512 à 515 | BASIC | Entreposage vectoriel d'interruption d'horloge segment:déplacement. | |

| 516 à 519 | BASIC | Entreposage de vecteur d'interruption de touche Break segment:déplacement. | |

| 51A à 51D | BASIC | Entreposage de vecteur d'interruption d'erreur disque segment:déplacement. | |

Si vous utilisez DEF SEG (segment d'espace de travail par défaut) :

| Déplacement (Valeur hexadécimal) | Longueur | Description | ||

|---|---|---|---|---|

| 2E | 2 | Numéro de ligne de la ligne courant d'exécution | ||

| 347 | 2 | Numéro de ligne de la dernière erreur | ||

| 30 | 2 | Déplacement dans le segment du début du texte du programme | ||

| 358 | 2 | Déplacement dans le segment du début des variables (fin du texte du programme 1-1) | ||

| 6A | 1 | Contenu de la mémoire tampon du clavier : | ||

| Valeur | Description | |||

| 0 | Pas de caractères dans le tampon | |||

| 1 | Un ou des caractères dans le tampon | |||

| 4E | 1 | Couleur des caractères en mode graphique : Définissez sur 1, 2 ou 3 pour obtenir le texte dans les couleurs 1 à 3. Ne définissez pas sur 0. (Par défaut = 3) |

||

| Adresse de départ en hexadécimal | Description |

|---|---|

| 00000 | Vecteur d'interruption BIOS |

| 00080 | Vecteurs d'interruption disponibles |

| 00400 | Zone de données du BIOS |

| 00500 | Mémoire de lecture/écriture utilisateur |

| C8000 | Adaptateur de disque |

| F0000 | Mémoire en lecture seulement |

| FE000 | Zone de programme BIOS |

Conseils de programmation du BIOS

Le code BIOS est invoqué via des interruptions logicielles. Le programmeur ne doit pas coder en dur les adresses BIOS dans les programmes d'application. Le fonctionnement interne et les adresses absolues dans le BIOS sont susceptibles d'être modifiés sans préavis. Si une erreur est signalée par le code du disque ou de la disquette, vous devez réinitialiser l'adaptateur de l'unité de disque et réessayer l'opération. Un nombre spécifié de tentatives doit être requis sur les lectures de disquette pour s'assurer que le problème n'est pas dû au démarrage du moteur. Lors de la modification des valeurs des bits du port d'entrée/sortie, le programmeur ne doit modifier que les bits nécessaires à la tâche en cours. À la fin, le programmeur doit restaurer l'environnement d'origine. Le non-respect de cette pratique peut être incompatible avec les applications présentes et futures.

Cartes adaptateurs avec modules ROM accessibles au système

La BIOS en ROM permet d'intégrer des cartes adaptatrices avec un code ROM intégré dans le système. Pendant le POST, des vecteurs d'interruption sont établis pour les appels BIOS. Une fois les vecteurs par défaut en place, une recherche de modules ROM supplémentaires a lieu. À ce stade, une routine ROM sur la carte adaptateur peut prendre le contrôle. La routine peut établir ou intercepter des vecteurs d'interruption pour s'accrocher au système. Les adresses absolues C8000 (en hexadécimal) à F4000 (en hexadécimal) sont balayées par blocs de 2 Ko à la recherche d'une ROM de carte adaptateur valide. Une ROM valide est définie comme suit :

| Déplacement | Description |

|---|---|

| Octet 0 | Valeur hexadécimal 55 |

| Octet 1 | Valeur hexadécimal AA |

| Octet 2 | Un indicateur de longueur représentant le nombre de blocs de 512 octets dans la ROM (longueur/512). Une somme de contrôle est également effectuée pour tester l'intégrité du module ROM. Chaque octet de la ROM définie est additionné modulo hexadécimal 100. Cette somme doit être 0 pour que le module soit considéré comme valide. |

Lorsque le POST identifie une ROM valide, il effectue un appel distant à l'octet 3 de la ROM devant être un code exécutable). La carte adaptateur peut maintenant effectuer ses tâches d'initialisation à la mise sous tension. La fonction ROM doit rendre le contrôle aux routines du BIOS en exécutant un retour FAR.

Encodage et utilisation du clavier

Codage : La routine de clavier fournie par IBM dans le BIOS en ROM est responsable de la conversion des codes de balayage du clavier en ce qui sera appelé «ASCII étendu». L'ASCII étendu comprend des codes de caractères à un octet avec des valeurs possibles de 0 à 255, un code étendu pour certaines fonctions de clavier étendues et des fonctions gérées dans la routine de clavier ou via des interruptions.

Codes de caractères : Les codes de caractères suivants sont transmis via la routine de clavier du BIOS au système ou au programme d'application. A '-1' signifie que la combinaison est supprimée dans la routine du clavier. Les codes sont retournés dans le registre AL.

| Numéro de touche | Minuscule | Majuscule | Ctrl | Alt |

|---|---|---|---|---|

| 1 | Esc | Esc | Esc | -1 |

| 2 | 1 | ! | -1 | Note 1 |

| 3 | 2 | @ | Nul (000) Note 1 | Note 1 |

| 4 | 3 | # | -1 | Note 1 |

| 5 | 4 | $ | -1 | Note 1 |

| 6 | 5 | % | -1 | Note 1 |

| 7 | 6 | " | RS(030) | Note 1 |

| 8 | 7 | & | -1 | Note 1 |

| 9 | 8 | * | -1 | Note 1 |

| 10 | 9 | ( | -1 | Note 1 |

| 11 | 0 | ) | -1 | Note 1 |

| 12 | - | - | US(031) | Note 1 |

| 13 | = | + | -1 | Note 1 |

| 14 | Backspace (008) | Backspace (008) | Del (127) | -1 |

| 15 | -1(009) | →|(Note 1) | |←-1 | -1 |

| 16 | q | Q | DC1 (017) | Note 1 |

| 17 | w | W | ETB (023) | Note 1 |

| 18 | e | E | ENG (005) | Note 1 |

| 19 | r | R | DC2(018) | Note 1 |

| 20 | t | T | DC4 (020) | Note 1 |

| 21 | y | Y | EM (025) | Note 1 |

| 22 | u | U | NAK (021) | Note 1 |

| 23 | i | I | HT (009) | Note 1 |

| 24 | 0 | 0 | SI (015) | Note 1 |

| 25 | p | P | DLE (016) | Note 1 |

| 26 | [ | { | Esc (027) | -1 |

| 27 | 1 | } | GS (029) | -1 |

| 28 | CR | CR | LF (010) | -1 |

| 29 Ctrl | -1 | -1 | -1 | -1 |

| 30 | a | A | SOH (001) | Note 1 |

| 31 | s | S | DC3 (019) | Note 1 |

| 32 | d | D | EOT (004) | Note 1 |

| 33 | f | F | ACK (006) | Note 1 |

| 34 | 9 | G | BEL (007) | Note 1 |

| 35 | h | H | BS (008) | Note 1 |

| 36 | j | J | LF (010) | Note 1 |

| 37 | k | K | VT(011) | Note 1 |

| 38 | l | L | FF (012) | Note 1 |

| 39 | : | - | 1 | -1 |

| 40 | ' | " | -1 | -1 | 41 | ` | ~ | -1 | -1 |

| 42 Shift | -1 | -1 | -1 | -1 |

| 43 | \ | I | FS (028) | -1 |

| 44 | z | Z | SUB (026) | Note 1 |

| 45 | x | X | CAN (024) | Note 1 |

| 46 | c | C | ETX (003) | Note 1 |

| 47 | v | V | SYN (022) | Note 1 |

| 48 | b | B | STX (002) | Note 1 |

| 49 | n | N | SO (014) | Note 1 |

| 50 | m | M | CR (013) | Note 1 |

| 51 | , | < | -1 | -1 |

| 52 | . | > | -1 | -1 |

| 53 | / | ? | -1 | -1 |

| 54 Shift | -1 | -1 | -1 | -1 |

| 55 | * | (Note 2) | (Note 1) | -1 |

| 56 Alt | -1 | -1 | -1 | -1 |

| 57 | SP | SP | SP | SP |

| 58 Caps Lock | -1 | -1 | -1 | -1 |

| 59 | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) |

| 60 | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) |

| 61 | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) |

| 62 | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) |

| 63 | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) |

| 64 | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) |

| 65 | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) |

| 66 | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) |

| 67 | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) |

| 68 | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) | Nul (Note 1) |

| 69 Num Lock | -1 | -1 | Pause (Note 2) | -1 |

| 70 Scroll Lock | -1 | -1 | Break (Note 2) | -1 |

| 1. Codes étendus 2. Manipulation spéciale |

||||

Les touches 71 à 83 n'ont de sens que dans le cas de base, dans les états Num Lock (ou décalé) ou dans l'état Ctrl. Notez que la touche Shift inverse temporairement l'état actuel de Num Lock.

| Numéro de touche | Num Lock | Touche | Alt | Ctrl |

|---|---|---|---|---|

| 71 | 7 | Home (Note 1) | -1 | Efface l'écran |

| 72 | 8 | ↑ (Note 1) | -1 | -1 |

| 73 | 9 | Page Up (Note 1) | -1 | Haut du texte et Home |

| 74 | - | ------------------------ | -1 | -1 |

| 75 | 4 | ← (Note 1) | -1 | Inverse le mot (Note 1) |

| 76 | 5 | -1 | -1 | -1 |

| 77 | 6 | → (Note 1) | -1 | Avance le mot (Note 1) |

| 78 | + | + | -1 | -1 |

| 79 | 1 | End (Note 1) | -1 | Efface à EOL (Note 1) |

| 80 | 2 | , | (Note 1) -1 | -1 |

| 81 | 3 | Page Down (Note 1) | -1 | Efface à EOS (Note 1) |

| 82 | 0 | Ins | -1 | -1 |

| 83 | Del (Notes 1,2) | Note 2 | Note 2 | |

| 1. Codes étendus 2. Manipulation spéciale |

||||

Codes étendus

Fonctions étendues : Pour certaines fonctions qui ne peuvent pas être représentées dans le code ASCII standard, un code étendu est utilisé. Un code de caractère de 000 (Nul) est renvoyé dans le registre AL. Cela indique que le système ou le programme d'application doit examiner un deuxième code indiquant la fonction réelle. Habituellement, mais pas toujours, ce deuxième code est le code de balayage de la touche primaire ayant été enfoncée. Ce code est renvoyé dans le registre AH.

| Second code | Fonction |

|---|---|

| 3 | Caractère nulle |

| 15 | ← |

| 16 à 25 | Alt Q, W, E, R, T, Y, U, I, O, P |

| 30 à 38 | Alt A, S, D, F, G, H, J, K, L |

| 44 à 50 | Alt Z, X, C, V, B, N, M |

| 59 à 68 | Cas de base des touches de fonction F1 à F10 |

| 71 | Home |

| 72 | ↑ |

| 73 | Page Up et Home Cursor |

| 75 | ← |

| 77 | → |

| 79 | End |

| 80 | ↓ |

| 81 | Page Down et Home Cursor |

| 82 | Ins (Insert) |

| 83 | Del (Delete) |

| 84 à 93 | F11 à F20 (Majuscule F1 à F10) |

| 94 à 103 | F21 à F30 (Ctrl F1 à F10) |

| 104 à 113 | F31 à F40 (Alt F1 à F10) |

| 114 | Ctrl PrtSc (Start/Stop Écho à imprimante) |

| 115 | Ctrl ← (Mot inverse) |

| 116 | Ctrl → (Mot avancé) |

| 117 | Ctrl End [Efface la fin de la ligne (EOL)] |

| 118 | Ctrl PgDn [Efface la fin de l'écran (EOS)] |

| 119 | Ctrl Home (Efface l'écran et l'accueil) |

| 120 à 131 | Alt 1,2,3,4,5,6,7,8,9,0, -, = (Touches 2 à 13) |

| 132 | Ctrl PgUp (25 premières lignes de texte et curseur d'accueil) |