Introduction

Le microprocesseur 80386DX de l'entreprise Intel est le premier microprocesseur 32 bits de la famille des 80x86. Il est parfois surnommé le i386DX ou i80386DX. Aussi, sur les puces électronique, il est plutôt écrit A80386 ou A80386DX. Il est le successeur des microprocesseur 80286 d'Intel. Grâce au microprocesseur 80386DX comble sont retard face à son concurrent MC68020 de Motorola sortie un an plus tôt utilisé par de nombreux rivaux des compatibles PC. Le premier compatible PC ayant proposé se microprocesseur fut le Compaq 386, bien avant qu'il soit utilisé dans la famille des PS/2 d'IBM. Le jeu d'instructions est compatible avec les microprocesseur 8086, 8088 et 80286 et en plus il fait l'intégration de nombreux registres 32 bits pouvant être traiter aussi bien en 8 bits, 16 bits qu'en 32 bits selon les besoins des programmes l'utilisant.

Peu de logiciel ou de système d'exploitation exploite vraiment les caractéristiques 32 bits du microprocesseur 80386DX à part le système d'exploitation UNIX ou OS/2 2.0 d'IBM. Enfin, l'environnement graphique DESQview/X 2.1 de Quarterdeck et les systèmes d'exploitation Windows 95 et Windows NT 3.51 de Microsoft arrivèrent tardivement en 1995 pour exploiter pleinement le 32 bits de cette puce électronique, soit 10 ans plus tard après sa conception !

Fiche technique

Voici les caractéristiques de la puce «80386DX» de l'entreprise «Intel»:

| Spécification | Description |

|---|---|

| Concepteur | Intel |

| Modèle | 80386DX |

| Date de conception | 1985 |

| Bus de données | 32 bits |

| Bus d'adressage | 32 bits |

| Nombre de transistors | 275000 |

| Alimentation | 5 volts |

| Jeu d'instructions | i386 DX |

| Architecture | IA-32 |

| Cadencé à | 16 Mhz, 20 Mhz, 25 Mhz ou 33 Mhz |

Liste des modèles

Voici les différents modèles de 80386DX :

| Numéro de modèle | Cadence | Coeur | Socket | Date de réalisation |

|---|---|---|---|---|

| A80386DX-16 | 16 MHz | 1 | PGA-132 de céramique | 1985 |

| A80386DX-20 | 20 MHz | 1 | PGA-132 de céramique | 1987 |

| A80386DX-20 IV | 20 MHz | 1 | PGA-132 de céramique | 1987 |

| A80386DX-25 IV | 25 MHz | 1 | PGA-132 de céramique | 1988 |

| A80386DX-33 IV | 33 MHz | 1 | PGA-132 de céramique | 1989 |

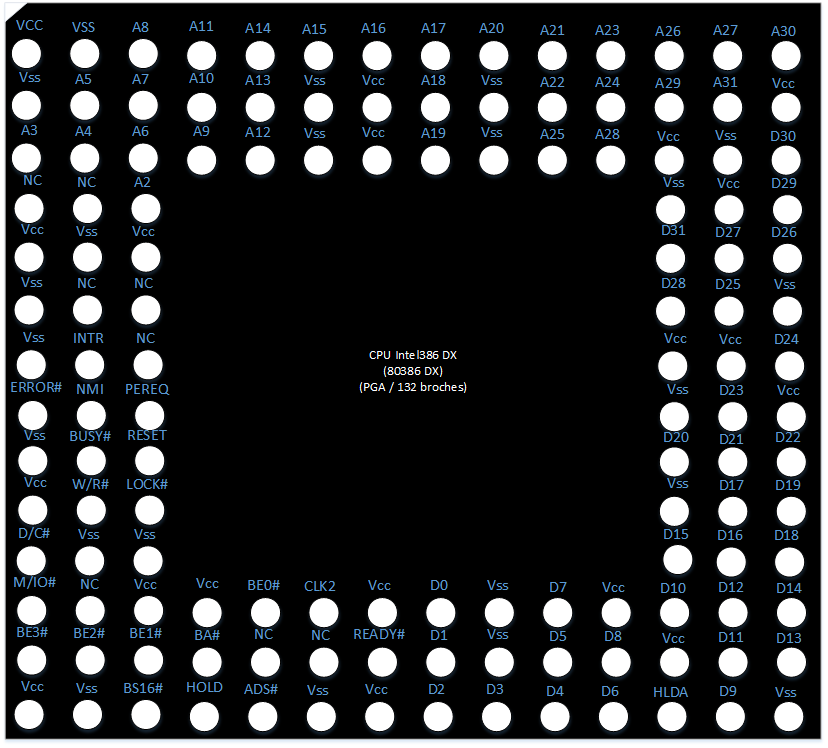

Schéma des broches

Voici le schéma des broches de la puce 80386DX de l'entreprise Intel :

Organisation de la mémoire

La mémoire sur le bus d'un microprocesseur 80386DX est appelée mémoire physique. Il est organisé comme une séquence d'octets de 8 bits. Une adresse unique, appelée adresse physique, est attribuée à chaque octet, allant de zéro à un maximum de 232-1 (4 gigaoctets). La gestion de la mémoire est un mécanisme matériel permettant une utilisation fiable et efficace de la mémoire. Lorsque la gestion de la mémoire est utilisée, les programmes ne s'adressent pas directement à la mémoire physique. Les programmes s'adressent à un modèle de mémoire, appelé mémoire virtuelle. La gestion de la mémoire consiste en une segmentation et une pagination. La segmentation est un mécanisme permettant de fournir plusieurs espaces d'adressage indépendants. La pagination est un mécanisme permettant de prendre en charge un modèle d'espace d'adresse volumineux dans la RAM utilisant une petite quantité de RAM et un peu d'entreposage sur disque. L'un ou l'autre de ces mécanismes peut être utilisé. Une adresse émise par un programme est une adresse logique. Le matériel de segmentation convertit une adresse logique en une adresse pour un espace d'adressage continu et non segmenté, appelé adresse linéaire. Le matériel de pagination convertit une adresse linéaire en une adresse physique. La mémoire peut apparaître comme un seul espace adressable, comme la mémoire physique. Ou bien, il peut apparaître comme un ou plusieurs espaces mémoire indépendants, appelés segments. Des segments peuvent être assignés spécifiquement pour contenir le code d'un programme (instructions), des données ou une pile. En fait, un seul programme peut comporter jusqu'à 16 383 segments de tailles et de types différents. Les segments peuvent être utilisés pour accroître la fiabilité des programmes et des systèmes. Par exemple, la pile d'un programme peut être placée dans un segment différent de celui de son code pour l'empêcher de se développer dans l'espace de code et d'écraser les instructions avec des données. Que des segments soient utilisés ou non, les adresses logiques sont converties en adresses linéaires en les traitant comme un déplacement dans un segment. Chaque segment a un descripteur de segment, conservant son adresse de base et sa taille limite. Si le déplacement ne dépasse pas la limite et qu'il n'existe aucune autre condition empêchant la lecture du segment, le déplacement et l'adresse de base sont additionnés pour former l'adresse linéaire. L'adresse linéaire produite par la segmentation est utilisée directement comme adresse physique si le bit 31 du registre CR0 est vide. Ce bit de registre contrôle si la pagination est utilisée ou non. Si le bit est défini, le matériel de pagination est utilisé pour convertir l'adresse linéaire en adresse physique. Le matériel de pagination donne un autre niveau d'organisation à la mémoire. Il divise l'espace d'adressage linéaire en blocs fixes de 4 Ko, appelés pages. L'espace d'adressage logique est cartographié dans l'espace d'adressage linéaire, étant cartographié sur un certain nombre de pages. Une page peut être en mémoire ou sur le disque. Lorsqu'une adresse logique est émise, elle est convertie en adresse pour une page en mémoire ou une exception est émise. Une exception donne au système d'exploitation une chance de lire la page à partir du disque et de mettre à jour la cartographie de page. Le programme ayant généré l'exception peut alors être redémarré sans générer d'exception. Si plusieurs segments sont utilisés, ils font partie de l'environnement de programmation vu par les programmeurs d'applications. Si la pagination est utilisée, elle est normalement invisible pour le programmeur d'application. Il devient visible uniquement en cas d'interaction entre le programme d'application et l'algorithme de pagination utilisé par le système d'exploitation. Lorsque toutes les pages en mémoire sont utilisées, le système d'exploitation utilise son algorithme de pagination pour décider quelles pages en mémoire doivent être envoyées sur le disque. Tous les algorithmes de pagination (à l'exception des algorithmes aléatoires) ont une sorte de comportement dans le pire des cas pouvant être exercé par certains types de programmes d'application. L'architecture du microprocesseur 80386DX offre aux concepteurs la liberté de choisir un modèle de mémoire différent pour chaque programme, même lorsque plusieurs programmes sont exécutés simultanément. Le modèle d'organisation de la mémoire peut varier entre les extrêmes suivants :

- Un espace d'adressage flat où les espaces de code, de pile et de données sont cartographiés aux mêmes adresses linéaires. Dans la mesure du possible, cette situation élimine la segmentation en permettant à tout type de référence de mémoire d'accéder à tout type de données.

- Un espace d'adressage segmenté avec des segments séparés pour le code, les données et les espaces de pile. Vous pouvez utiliser jusqu'à 16 383 espaces d'adresses linéaires de 4 Go chacun.

Les deux modèles peuvent fournir une protection de la mémoire. Des modèles intermédiaires entre ces extrêmes peuvent également être choisis.

Types de données

Les octets, les mots et les doubles mots sont les principaux types de données. Un octet est 8 bits. Les bits sont numérotés de 0 à 7, le bit 0 étant le bit le moins significatif (LSB). Un mot est 2 octets occupant 2 adresses consécutives. Un mot contient 16 bits. Les bits d'un mot sont numérotés de 0 à 15, le bit 0 étant le bit le moins significatif. L'octet contenant le bit 0 du mot s'appelle l'octet bas; l'octet contenant le bit 15 est appelé l'octet haut. Sur le microprocesseur 80386DX, l'octet de poids faible est entreposé dans l'octet avec l'adresse inférieure. L'adresse de l'octet de poids faible est également l'adresse du mot. L'adresse de l'octet de poids fort n'est utilisée que lorsque la moitié supérieure du mot est utilisée séparément de la moitié inférieure. Un double mot est constitué de 4 octets occupant 4 adresses consécutives. Un double mot contient 32 bits. Les bits d'un double mot sont numérotés de 0 à 31, le bit 0 étant à nouveau le bit le moins significatif. Le mot contenant le bit 0 du double mot est appelé le mot bas; le mot contenant le bit 31 s'appelle le mot haut. Le mot faible est entreposé dans les 2 octets avec les adresses inférieures. L'adresse de l'octet le plus bas est l'adresse du double mot. Les adresses les plus élevées ne sont utilisées que lorsque le mot supérieur est accédé séparément du mot inférieur ou lorsque des octets individuels sont utilisés. Notez que les mots n'ont pas besoin d'être alignés sur des adresses paires et que les mots doubles ne doivent pas être alignés sur des adresses divisibles par 4. Cette situation permet une flexibilité maximale dans les structures de données (par exemple, les enregistrements contenant des éléments mélangés d'octets, de mots et de mots doubles) et une utilisation efficace de la mémoire. Le microprocesseur 80386DX étant doté d'un bus de données de 32 bits, la communication entre le microprocesseur et la mémoire s'effectue par transfert double mot aligné sur des adresses divisibles par 4; le microprocesseur convertit les transferts de double mot alignés sur d'autres adresses en plusieurs transferts. Ces opérations non alignées réduisent la vitesse en exigeant des cycles de bus supplémentaires. Pour une vitesse maximale, les structures de données (en particulier les piles) doivent être conçues de manière à ce que, chaque fois que cela est possible, les opérandes de mots soient alignés sur des adresses paires et les opérandes de mots doubles à des adresses divisibles par 4. Bien que les octets, les mots et les doubles mots soient les types fondamentaux d'opérandes, le microprocesseur prend également en charge des interprétations supplémentaires de ces opérandes. Les instructions spécialisées reconnaissent les types de données suivants :

| Type de données | Description |

|---|---|

| Entier (integer) | Ce type de données est un nombre binaire signé contenu dans un double mot, un mot de 16 bits ou un octet de 8 bits de 32 bits. Toutes les opérations supposent une représentation du complément à 2. Le bit de signe est situé dans le bit 7 dans un octet, dans le bit 15 dans un mot et dans le bit 31 dans un double mot. Le bit de signe est défini pour les entiers négatifs, tandis que le bit est effacé pour les entiers positifs et zéro. La valeur d'un entier de 8 bits est comprise entre -128 et +127; un entier de 16 bits compris entre -32 768 et +32 767; un entier de 32 bits compris entre - 231 et +231-1. |

| Ordinal | Ce type de données est un nombre binaire non signé contenu dans un mot double, un mot de 16 bits ou un octet de 8 bits de 32 bits. La valeur d'un ordinal à 8 bits est comprise entre 0 et 255; un ordinal de 16 bits de 0 à 65 535; un ordinal de 32 bits de 0 à 232-1. |

| Pointeur court (Near Pointer) | Ce type de données est une adresse logique de 32 bits. Un pointeur court est un déplacement dans un segment. Les pointeurs court sont utilisés pour tous les pointeurs dans un modèle de mémoire à flat ou pour les références au sein d'un segment dans un modèle segmenté. |

| Pointeur long (Far Pointer) | Ce type de données est une adresse logique à 48 bits composée d'un sélecteur de segment de 16 bits et d'un déplacement de 32 bits. Les pointeurs long sont utilisés dans un modèle de mémoire segmentée pour accéder à d'autres segments. |

| Chaîne de caractères | Ce type de données est une séquence contiguë d'octets, de mots ou de doubles mots. Une chaîne de caractères peut contenir de 0 à 232-1 octets (4 gigaoctets). |

| Champ de bits | Ce type de données est une séquence de bits contigus. Un champ de bits peut commencer à n'importe quelle position de bit d'un octet et peut contenir jusqu'à 32 bits. |

| Chaîne de bits | Ce type de données est une séquence de bits contigus. Une chaîne de bits peut commencer à n'importe quelle position de bit de tout octet et peut contenir jusqu'à 232-1 bits. |

| BCD | Ce type de données est une représentation d'un chiffre décimal codé binaire (BCD) compris entre 0 et 9. Les nombres décimaux non empaquetés sont entreposés sous forme de quantités d'octets non signés. Un chiffre est entreposé dans chaque octet. La magnitude du nombre est la valeur binaire du demi-octet d'ordre faible; les valeurs 0 à 9 sont valides et sont interprétées comme la valeur d'un chiffre. Le demi-octet d'ordre élevé doit être égal à zéro pendant la multiplication et la division; il peut contenir n'importe quelle valeur pendant l'addition et la soustraction. |

| BCD empaquetés | Ce type de données est une représentation des chiffres décimaux codés en binaire, chacun dans la plage de 0 à 9. Un chiffre est entreposé dans chaque demi-octet, deux chiffres dans chaque octet. Le chiffre des bits 4 à 7 est plus significatif que le chiffre des bits 0 à 3. Les valeurs 0 à 9 sont valables pour un chiffre. |

Les registres

Le microprocesseur 80386DX contient 16 registres pouvant être utilisés par un programmeur d'application. Ces registres peuvent être regroupés comme suit :

- Registres généraux : Ces 8 registres de 32 bits sont libres d'utilisation pour le programmeur.

- Registres de segments : Ces registres contiennent des sélecteurs de segments associés à différentes formes d'accès à la mémoire. Par exemple, il existe des registres de segments distincts pour l'accès au code et à l'espace de pile. Ces 6 registres déterminent, à tout moment, quels sont les des segments de mémoire sont actuellement disponibles.

- Registres d'état et de contrôle : Ces registres indiquent et permettent la modification de l'état du microprocesseur 80386DX.

Format d'instruction

Les informations codées dans une instruction comprennent une spécification de l'opération à effectuer, du type des opérandes à manipuler et de l'emplacement de ces opérandes. Si un opérande est situé en mémoire, l'instruction doit également sélectionner, explicitement ou implicitement, le segment contenant l'opérande. Une instruction peut avoir différentes parties et formats. Les parties d'une instruction sont décrites ci-dessous. De ces parties, seul l'opcode est toujours présent. Les autres parties peuvent être présentes ou non, en fonction de l'opération impliquée, de l'emplacement et du type des opérandes. Les parties d'une instruction, par ordre d'occurrence, sont énumérées ci-dessous :

- Préfixe : un ou plusieurs octets précédant une instruction, qui en modifient le fonctionnement. Les préfixes suivants peuvent être utilisés par les programmes d'application :

- Opcode : spécifie l'opération effectuée par l'instruction. Certaines opérations ont plusieurs codes d'opération différents, chacun spécifiant une forme différente de l'opération.

- Spécificateur de registre : une instruction peut spécifier 1 ou 2 opérandes de registre. Les spécificateurs de registre apparaissent dans le même octet que le code d'opération ou dans le même octet que le spécificateur de mode d'adressage.

- Spécificateur de mode d'adressage : spécifie, le cas échéant, si un opérande est un registre ou un emplacement de mémoire; si en mémoire, spécifie si un déplacement, un registre de base, un registre d'index et une mise à l'échelle doivent être utilisés.

- Octet SIB (échelle, index, base) : lorsque le spécificateur de mode d'adressage indique qu'un registre d'index sera utilisé pour calculer l'adresse d'un opérande, un octet SIB est inclus dans l'instruction permettant de coder le registre de base, le registre d'index, et un facteur d'échelle.

- Déplacement : lorsque le spécificateur de mode d'adressage indique qu'un déplacement sera utilisé pour calculer l'adresse d'un opérande, le déplacement est codé dans l'instruction. Un déplacement est un entier signé de 32, 16 ou 8 bits. La forme à 8 bits est utilisée dans le cas commun lorsque le déplacement est suffisamment petit. Le microprocesseur étend un déplacement de 8 bits à 16 ou 32 bits, en tenant compte du signe.

- Opérande immédiat : lorsqu'il est présent, fournit directement la valeur d'un opérande. Les opérandes immédiats peuvent être des octets, des mots ou des mots doubles. Dans les cas où un opérande immédiat de 8 bits est utilisé avec un opérande de 16 ou 32 bits, le microprocesseur étend l'opérande de 8 bits à un entier du même signe et de la même grandeur dans la taille la plus grande. De la même manière, un opérande de 16 bits est étendu à 32 bits.

- Un remplacement de segment spécifique explicitement le registre de segment qu'une instruction doit utiliser à la place du registre de segment par défaut.

- La taille de l'adresse bascule entre un adressage de 16 et 32 ??bits. La taille peut être la valeur par défaut, ce préfixe sélectionne la taille autre que celle par défaut.

- La taille d'opérande permet de basculer entre la taille de données 16 et 32 ??bits. La taille peut être la valeur par défaut, ce préfixe sélectionne la taille autre que celle par défaut.

- Un répéteur utilisé avec une instruction de chaîne pour que l'instruction soit répétée pour chaque élément de la chaîne.

Sélection de l'opérateur

Une instruction agit sur 0 ou plusieurs opérandes. Un exemple d'instruction zéro-opérande est l'instruction NOP (aucune opération). Un opérande peut être tenu dans n'importe lequel de ces endroits :

- dans l'instruction même (un opérande immédiat).

- dans un registre (dans le cas d'opérandes 32 bits, EAX, EBX, ECX, EDX, ESI, EDI, ESP ou EBP; dans le cas d'opérandes 16 bits AX, BX, CX, DX, SI, DI, SP ou BP; dans le cas d'opérandes AH, AL, BH, BL, CH, CL, DH ou DL, les registres de segments ou le registre EFLAGS pour les opérations d'indicateur). L'utilisation d'opérandes de registre 16 bits nécessite l'utilisation du préfixe de taille d'opérande 16 bits (un octet avec la valeur 67h précédant l'instruction).

- En mémoire.

- sur un port d'entrée/sortie.

Les opérandes immédiats et les opérandes dans les registres sont accessibles plus rapidement que les opérandes en mémoire car les opérandes en mémoire nécessitent des cycles de bus supplémentaires. Les opérandes de registre et immédiats sont disponibles sur la puce, ces derniers étant pré-lus lors de l'interprétation de l'instruction.

Interruptions et exceptions

Le microprocesseur 80386DX dispose de 2 mécanismes pour interrompre l'exécution du programme :

- Les exceptions sont les événements synchrones constituant les réponses du microprocesseur à certaines conditions détectées lors de l'exécution d'une instruction.

- Les effets intenses sont des événements désynchronisés généralement déclenchés par des périphériques externes nécessitant une intervention.

Les interruptions et les exceptions sont semblables en ce sens que le microprocesseur suspend temporairement le programme en cours d'exécution afin d'exécuter un programme de priorité supérieure. La principale distinction entre ces deux types d'interruptions est leur origine. Une exception est toujours reproductible en ré-exécutant le programme ayant provoqué l'exception, alors qu'une interruption peut avoir une relation complexe, dépendant de laps de temps, avec les programmes.

Programmation

| Langage | Description |

|---|---|

| Assembleur 80x86 | Langage Assembleur pour la famille des microprocesseurs 80x86 |